# 一种有效的低功耗扫描测试结构——PowerCut

王  $f^{12}$  韩银和<sup>23</sup> 胡  $\mathfrak{m}^{23}$  李晓维<sup>23</sup> 张佑生

- 1(合肥工业大学计算机与信息学院 合肥 230009)

- ?(中国科学院计算技术研究所先进测试技术实验室 北京 100080)

- 3(中国科学院计算技术研究所系统结构重点实验室 北京 100080)

(wang\_wei@ict.ac.cn)

#### An Effective Low-Power Scan Architecture—PowerCut

Wang Wei<sup>1 2</sup>, Han Yinhe<sup>2 3</sup>, Hu Yu<sup>2 3</sup>, Li Xiaowei<sup>2 3</sup>, and Zhang Yousheng<sup>1</sup>

- <sup>1</sup>(School of Computer and Information , Hefei University of Technology , Hefei 230009)

- <sup>2</sup>(Advanced Test Technology Laboratory , Institute of Computing Technology , Chinese Academy of Sciences , Beijing 100080)

- <sup>3</sup>(State Key Laboratory of Computer Architecture, Institute of Computing Technology, Chinese Academy of Sciences, Beijing 100080)

Abstract It is obvious that scan testing is the prevalent design for testability (DFT) in very large scale integrated circuits test. However, scan architecture in digital circuits causes much power consumption because when scan vectors are loaded into a scan chain, the effect of scan-ripple propagates to the combinational logic and redundant switching occurs in the combinational gates during the entire vectors shifting period. Hence, low-power design becomes a challenge for scan test. In this paper, a low-power scan architecture—PowerCut is proposed for minimizing power consumption during scan test, which is based on scan chain modification techniques. Blocking logic using transmission gates is inserted into the scan chain to reduce the dynamic power in shift cycle. At the same time, based on minimum leakage vector, a controlling unit is inserted. It makes the circuit slip into low leakage state during shift cycle. Thus, leakage power is also decreased. Experiments results indicate that this architecture can effectually reduce the power during scan test, and it has little improvement in area or delay overhead, compared with other low cost existing methods.

Key words test power; blocking logic; controlling unit; scan chain

摘 要 扫描测试是超大规模集成电路测试中最常用的一种技术. 但在扫描测试过程中,扫描单元的频繁翻转会引起电路中过大的测试功耗,这对电路测试提出了新的挑战. 提出了一种新颖的低功耗全扫描结构——PowerCut,通过对扫描链的修改,加入阻隔逻辑,有效降低扫描移位过程中的动态功耗,同时加入控制单元,使电路在扫描移位过程时进入低漏电流状态,降低了电路的静态功耗. 实验表明该结构在较小的硬件开销范围内有效地减小了扫描测试功耗.

关键词 测试功耗 :阻隔逻辑 :控制单元 :扫描链

中图法分类号 TP391.76

片上系统(system on a chip, SOC)的发展对集成电路的设计和测试均提出了多方面的挑战,而测

试时的高功耗就是其中非常重要的一项.由于测试向量的低关联性特征,使得测试状态下电路中的

收稿日期 2006-02-27 ;修回日期 2006-08-22

跳变远远多于正常工作状态,这时的功耗比正常工作情况下高得多,甚至可能达到正常情况下的2倍以上[1].目前,高速的并行测试是SOC测试的发展趋势,但是随之而来的是巨大的测试功耗.而对于使用BIST的设备来说,过大的测试功耗会使便携式设备的电池加快损耗,降低移动设备的电源支持时间.更重要的是目前的集成电路系统大多采用低功耗设计,电路某些器件很可能不能承受测试时过大的功耗,对器件造成破坏,降低成品率,增加芯片成本.

扫描测试是目前最常用的一种可测试性设计方 法 触发器被串成扫描链的形式 待测电路也被相应 划分为扫描链和组合逻辑两部分. 扫描测试时,电 路的功耗也就由这两部分的功耗组成,其中组合逻 辑中产生的功耗会占到总功耗的 78% 左右[2]. 此 外 扫描测试分为向量在扫描链的移位周期(shift cvcle )和测试响应的捕捉周期(capture cvcle). 在测 试向量移位进入扫描链和测试响应向量移出扫描链 的周期中,一方面,扫描链上值的变化仍然会使组合 逻辑中发生大量跳变,而这些跳变引起了巨大能量 的无谓消耗,这属于动态功耗部分.另一方面,随着 生产工艺水平的提高 ,工艺尺寸的下降 ,静态功耗在 总功耗中所占的比重越来越大,已证明在 90nm 工 艺下,静态功耗将占整个电路实际消耗功耗的 42% 以上[3]. 综上所述,同时减小待测电路组合逻辑部 分的动态功耗和静态功耗已经成为实现低功耗测试 的关键.

扫描测试的功耗优化问题已经成为一个研究的热点. Butler 等人<sup>[4]</sup>通过 ATPG 与可测试性设计相结合的方法进行功耗优化. Rosinger 等人<sup>[5]</sup>使用了多条扫描链配合电路划分来减小峰值功耗,但代价是测试时间大大延长. Orailoglu 等人<sup>[6]</sup>通过在扫描链中插入逻辑门的方法使扫描链的翻转尽可能的少. Gerstendorfer<sup>[2]</sup>使用 NOR 或 NAND 对扫描链和组合逻辑进行隔离. Bushnel<sup>[7]</sup>和 Zhang<sup>[8]</sup>等人则在移位周期内分别利用锁存器和多路器对扫描单元的输出进行阻隔. Bhunia 等人<sup>[9]</sup>在晶体管级对电路进行了修改,用较小的时延和面积开销实现了功耗优化,但大规模修改电路的不同逻辑单元在实际生产中的实现难度较大. 上述的各种方法,主要都是为了使扫描链在移位过程中少引起或不引起组合逻辑部分的跳变,降低动态测试功耗.

另一方面,低功耗设计技术中也有很多通过漏 电流控制技术[10]来降低静态功耗的方法.输入向量 控制方法通过最小漏电流向量(minimum leakage vector MLV  $\}$  <sup>11</sup> <sup>1</sup>控制电路进入低漏电流休眠状态.阈值电压控制法(threshold voltage control 和源级偏置法(source biasing  $\}$  <sup>12</sup> <sup>1</sup>能够降低由于亚阈值电流造成的漏电流问题,但是在一定程度上是以牺牲性能为代价.

本文提出了一种低功耗扫描测试结构——PowerCut,通过对扫描单元的修改,加入传输门实现阻隔逻辑(blocking logic),大幅减少扫描移位过程中的动态功耗,同时加入CMOS管以实现控制逻辑,使电路在扫描移位时进入低漏电流状态,有效降低了静态功耗.和上述提到的阻隔方法[2,7-9]相比,本文的方法在同样实现阻隔扫描链与组合逻辑的基础上,降低了电路的静态功耗,同时阻隔逻辑与控制逻辑的面积与时延开销较小,在大规模电路的实际生产中可以通过替换单一逻辑单元的方法快速实现.

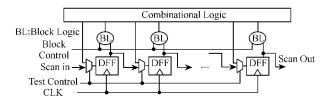

# 1 PowerCut 的阻隔逻辑设计

由于在测试向量的扫描移位过程中,扫描单元的输出仍然是逻辑单元的输入,因此扫描单元中值的变化仍然影响着组合逻辑,每一个时钟周期均引起组合逻辑状态的不断变化,产生了大量的动态功耗. 阻隔逻辑的作用就是在此过程中,使扫描链与组合逻辑实现逻辑隔离,避免扫描单元对组合逻辑的影响,从而降低动态测试功耗. 将阻隔逻辑施加到扫描单元的输出端(图1),在扫描移位时通过控制信号控制阻隔逻辑进入阻隔状态,使组合逻辑的输入保持稳定,这样就使组合逻辑状态在移位周期中不发生变化,没有动态功耗的损失. 而正常工作时,阻隔逻辑为透明状态,触发器与组合逻辑可以无障碍的通信.

Fig. 1 Sketch map of blocking logic. 图 1 阻隔结构示意图

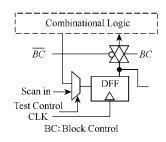

阻隔逻辑有多种实现方法,比如 NOR<sup>21</sup>,NAND<sup>21</sup>, Latch<sup>[7]</sup>,MUX<sup>[8]</sup>. 但是这些方法的面积开销相对较大,对时延的影响也较明显,这会影响正常工作状态下触发器与组合逻辑间的数据通信速度,甚至降低芯片的工作频率. 本文提出使用 PowerCut 结构对

扫描测试功耗进行优化,避免了上述方面的负面效果. PowerCut 中的阻隔逻辑部分设计如图 2 所示:

Fig. 2 Blocking logic in PowerCut.

图 2 PowerCut 中的阻隔结构

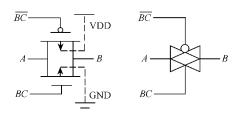

本文通过在扫描单元的输出端与组合逻辑的输入端之间增加一个 CMOS 传输门( transmission gate )来实现阻隔. 传输门是一种可控开关电路,它接近于一个理想的电子开关,开关接通时自身的电阻很小,而开关断开时其电阻很大. CMOS 传输门由一对互补 MOS 管组合而成(图 3 ),两管的源极相连作为输入端 A 漏极相连作为输出端 B. 两个栅极是一对互补控制端 ,分别接入控制信号 BC 和 $\overline{BC}$ . P管和 N 管的衬底分别接电源 VDD 和地端 GND . 传输门的开启和关闭是由互补脉冲控制的 ,当 BC=0 , $\overline{BC}=1$  时 ,传输门关闭 ,输出端 B 为高阻态(Z 态);当 BC=1 , $\overline{BC}=0$  时 ,传输门开启 ,A=B . 由于传输门的输入端和输出端是对称的 ,所以它们的源极和漏极能够互换使用 ,可以任意把其中一个作输入端 ,另一个作输出端 ,所以又称它为双向开关.

Fig. 3 Architecture of transmission gate.

图 3 传输门结构

测试中,当处于测试响应的捕捉周期时,需要传输门开启,以便扫描单元与组合逻辑进行数据交换.而在移位周期时,传输门则处于关闭状态,实现逻辑阻隔的作用,大大减小了被测电路在扫描移位时的动态功耗.正常工作状态时,传输门开启,为透明状态.

## 2 PowerCut 的控制单元设计

### 2.1 控制单元原理

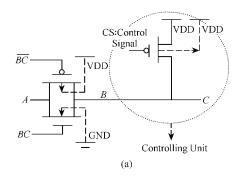

传输门关闭时,阻隔逻辑的输出端呈 Z 态,也就是说组合逻辑的输入为浮空状态,这会引起组合逻辑的逻辑混乱.所以必须使传输门关闭时,组合逻辑的输入能够稳定处于某一确定值.这就需要在阻隔逻辑上增加控制单元以使电路进入稳定状态.

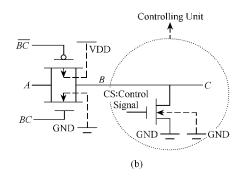

控制单元的设计如图 4 所示. 在传输门的输出端 B 增加一个 PMOS 管 ,见图 4(a),通过控制信号 CS(control signal)控制该 CMOS 管 ;另一种控制单元则是通过增加一个 NMOS 管以实现控制功能 ,见图 4(b).

举例说明图 4(a)上拉控制单元的控制机制:

- 1) 当传输门处于关闭状态、B 端处于高阻态时 将 control signal 赋值为逻辑 0 ,使 PMOS 管导通 将输出端 C 上拉为逻辑 1 . 此时 ,C=B=1 .

- 2) 当传输门处于透明状态时,控制 control signal 为逻辑 1 PMOS 管截止 C = B = A.

图 4( b)下拉控制单元的控制机制以此类推:

- 1)当传输门处于关闭状态、B 端处于高阻态时 将 control signal 赋值为逻辑 1,使 NMOS 管导通 将输出端 C 下拉为逻辑 0.此时 C=B=0.

- 2) 当传输门处于透明状态时,控制 control signal 为逻辑 0 ,NMOS 管截止,C = B = A.

Fig. 4 Architecture of controlling unit. (a) Pull-up controlling unit and (b) Pull-down controlling unit.

图 4 控制单元结构. (a) 上拉控制单元 (b) 下拉控制单元

#### 2.2 低漏电流扫描控制

根据晶体管的堆栈效应,在向量的移位周期中,组合逻辑的每种状态都将对应产生相应的漏电流,而漏电流又会产生一定的静态功耗<sup>11</sup>]. 因此,在测试中,测试向量直接决定着测试时电路的漏电流.测试向量由很多确定位(0或1)和不确定位(don't care bits,通常用 X表示)组成. 不确定位表示这一位的值可以是逻辑 0 也可以逻辑 1,但无论哪种赋值都不影响测试的故障覆盖率,对测试结果无影响.在实际测试时,通常对不确定位随意赋值. 一般来说,对于大规模电路,自动测试产生器(automatic test pattern generation,ATPG)产生的测试向量中不确定位大都在50%以上. 显而易见,如果对数量如此巨大的不确定位随意赋值很可能导致测试时电路中的漏电流过大,对电路造成负面影响.

对于小规模电路 ,对不确定位可以使用穷举的方法 ,找到对应测试时最小漏电流的不确定位赋值组合. 然而大规模电路往往有成百上千个输入 ,不可能用穷举的方法来解决这个 NP 问题( 假设 N 个不确定位 ,搜索空间即为  $2^N$  ). 这时采用启发性算法会收到较好的效果.

遗传算法(genetic algorithm GA)作为一种有效的最优化搜索方法,通用性、鲁棒性强,常被用来求解 NP-hard 问题. 利用遗传算法对不确定位的赋值空间进行快速搜索,可以得出产生最小漏电流的测试向量 X 位的赋值组合,也得到了最小漏电流测试向量(MLV).

为了使扫描移位时电路在产生最小动态功耗的同时,产生最小的漏电流和静态功耗,需要在阻隔逻辑发生作用的情况下,将得到的最小漏电流测试向量(MLV)施加到被测电路上.本文通过控制单元完成该功能.

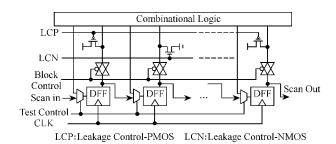

扫描移位时 ,参照 MLV ,控制单元控制相应的

扫描单元输出对应的逻辑值. PMOS 管负责输出一个稳定的逻辑 1, NMOS 管负责输出一个稳定的逻辑 0. 也就是说,根据最小漏电流测试向量中的 1或 0值,在对应的控制单元中采用相应的 PMOS 管或 NMOS 管,如图 5 所示. 而为了能够实现稳定而有效的上拉、下拉功能, PMOS 管和 NMOS 管的尺寸接近于相应最小晶体管尺寸的 10 倍<sup>19 1</sup>.

Fig. 5 PowerCut in CUT. 图 5 PowerCut 结构示意图

# 3 实验结果

本文实验使用了 90nm 工艺的 BPTM 模型 (Berkeley predictive technology model) <sup>13</sup> 进行功耗 分析 ,室温为 25℃. 我们采用 MINTEST<sup>[14]</sup>测试集 对部分 ISCAS85 和部分 ISCAS89 电路进行了实验 ,时延信息使用 Hspice 工具在 65nm 工艺下取得.

使用或非门(NOR)进行阻隔逻辑设计的方法是现有阻隔技术中较好的方法<sup>[9]</sup>.NOR由4个晶体管构成,而PowerCut方法同样的一个阻隔单元仅由3个晶体管构成.由于晶体管的数量与面积、功耗基本成正比,因此,通常情况下PowerCut的阻隔单元会比NOR有较小的面积开销和功耗开销.此外,PowerCut能够使待测电路在较长的扫描移位周期中进入低漏电流状态,使电路较长时间保持低静态测试功耗状态,这点是NOR方法不具备的.有关实验结果如表1、表2所示.

|     | Table 1 | PowerCut vs. | NOR   |

|-----|---------|--------------|-------|

| 表 1 | PowerCu | t 和基于 NOR    | 方法的比较 |

| Ckt.         | # gates     | # Elin Elin       | NOR Gating (mW) | DC(W)          | Improve in Leakage Power | Improve in Test Power |

|--------------|-------------|-------------------|-----------------|----------------|--------------------------|-----------------------|

| CKI. # gates | # rnp-riops | NOR Gating ( mw ) | rowercuit mw )  | Over NOR ( % ) | Over NOR (%)             |                       |

| S1238        | 428         | 18                | 0.44            | 0.42           | 6.53                     | 4.76                  |

| S5378        | 1004        | 179               | 3.40            | 3.25           | 15.01                    | 4.62                  |

| S9234        | 2027        | 211               | 4.98            | 4.62           | 16.32                    | 7.79                  |

| S13207       | 2573        | 638               | 21.87           | 20.65          | 17.55                    | 5.91                  |

| S15850       | 3448        | 534               | 20.65           | 19.03          | 10.17                    | 8.51                  |

| S35932       | 12204       | 1728              | 33.57           | 31.49          | 14.89                    | 6.61                  |

| S38584       | 11448       | 1426              | 53.23           | 48.99          | 15.05                    | 8.65                  |

|              |             |                   |                 |                |                          |                       |

Table 2 Comparison of Area and Delay Among

Some Gating Architecture

表 2 常用门控单元的面积开销、时延开销比较

| C .        | Gate   |       |          |  |

|------------|--------|-------|----------|--|

| Cost -     | Latch  | NOR   | PowerCut |  |

| Area (μm²) | 23.050 | 7.683 | 6.01     |  |

| Delay (ps) | 83.96  | 65.37 | 36.16    |  |

表1显示了 PowerCut 对测试功耗的优化效果好于利用 NOR 的阻隔方法. 在扫描单元数量较少、电路规模较小时,两者的效果差距并不明显,但随着扫描单元数量的增加、电路规模的扩大,PowerCut的优势非常明显. 而对于单个阻隔单元的实验(表2)表明,对于传统的使用 Latch 和 NOR 的阻隔方法,PowerCut 方法的面积开销具有优势,而在时延开销方面优势更加明显.

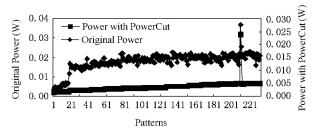

图 6 为使用了 PowerCut 方法的基准电路 s9234 在一个完整的移位周期和随后的测试响应捕捉周期 时功耗的示意图. 可以看出 ,PowerCut 有效地降低 了待测电路在移位周期中的平均功耗.

Fig. 6 Effect of PowerCut in s9234. 图 6 s9234 使用 PowerCut 的效果

# 4 结束语

本文提出了一种有效降低扫描移位周期中电路测试功耗的结构。该结构仅仅在每个扫描单元上增加3个晶体管,有效阻隔了移位周期中扫描单元的翻转对在组合逻辑的影响,大大降低了待测电路的动态功耗,同时使电路进入低漏电流的休眠状态,降低了此时的静态功耗。同时该结构还保持了测试的故障覆盖率,没有影响电路正常的测试工作。由于PowerCut与扫描单元的扇出数量没有固定的比例关系,因此当电路扫描单元平均扇出数大于1.5时,PowerCut的面积开销将小于文献[9],此时,PowerCut即成为目前所有此类方法中面积开销最小的方法.

### 参考文献

[1] Y Zorian. A distributed BIST control scheme for complex VLSI devices [C]. In: Proc of the IEEE VLSI Test Symposium. Los Alamitos, CA: IEEE Computer Society Press, 1993. 4-9

- [2] S Gerstendrfer, et al. Minimized power consumption for scan-based BIST[C]. In: Proc of the IEEE Int'l Test Conf (ITC). Los Alamitos, CA: IEEE Computer Society Press, 1999. 77–84

- [3] J Kao, S Narendra, A Chandrakasan. Subthreshold leakage modeling and reduction techniques [C]. In: Proc of the IEEE/ ACM Int 'l Conf on Computer-Aided Design (ICCAD). New York: ACM Press, 2002. 141-148

- [4] K M Butler, J Saxena, T Fryars, et al. Minimizing power consumption in scan testing: Pattern generation and DFT techniques[C]. In: Proc of the IEEE Int'l Test Conf (ITC). Los Alamitos, CA: IEEE Computer Society Press, 2004. 355– 364

- [5] P M Rosinger, B M Al-Hashimi, N Nicolici. Scan architectqure for shift and capture cycle power reduction [C]. IEEE Int'l Symp on Defect and Fault Tolerance in VLSI Systems (DFT), Vancouver, BC, Canada, 2002

- [6] O Sinanoglu, A Orailoglu. Scan power minimization through stimulus and response transformations [C]. IEEE Design, Automation and Test in Europe Conf and Exhibition (DATE), Paris, France, 2004

- [7] M L Bushnell , V D Agarwal. Essentials of Electronic Testing for Digital , Memory , and Mixed-signal VLSI Circuits [M]. Amsterdam , Netherlands: Kluwer Academic Publishers , 2000

- [8] X Zhang , K Roy. Power reduction in test-per-scan BIST[C]. IEEE Int 'l On-Line Testing Workshop , Palma de Mallorca , Spain , 2000

- [9] S Bhunia, H Mahmoodi, D Ghosh, et al. Low-power scan design using first-level supply gating [J]. IEEE Trans on Very Large Scale Integration Systems, 2005, 13(3):384–395

- [ 10 ] K Roy , S Mukhopadhyay , H Mahmoodi. Leakage current mechanisms and leakage reduction techniques in deep-submicron CMOS circuits [ J ]. Proceeding of the IEEE , 2003 , 91(2): 305-327

- [ 11 ] A Abdollahi , F Fallah , M Pedram. Leakage current reduction in CMOS VLSI circuits by input vector control [ J ]. IEEE Trans on Very Large Scale Integration Systems , 2004 , 12(2):140-

- [ 12 ] C Kim , K Roy. Dynamic VTH scaling scheme for active leakage power reduction [ C ]. IEEE/ACM Design , Automation and Test European Conf ( DATE ) , Paris , France , 2002

- [ 13 ] UC Berkeley Device Group [ OL ]. http://www-device.eecs.berkeley.edu/~ptm/, 2005-09-30/2005-12-01

- [ 14 ] I Hamzaoglu, J Patel. Test set compaction algorithms for combinational circuits [ C ]. IEEE/ACM Int 'l Conf on Computer-Aided Design ( ICCAD ), San Jose, CA, 1998

Wang Wei, born in 1979. Received his B. Eng. 's degree from Hefei University of Technology in 2001. He now is Ph. D. candidate also in Hefei University of Technology, and student member of China Computer Federation. His main research

interests include low power test , design-for-testability , and low power design.

王 伟,1979年生,博士研究生,中国计算机学会学生会员, 主要研究方向为低功耗测试技术、可测试性设计、低功耗 设计.

Han Yinhe, born in 1980. Received his B. Eng. 's degree from Nanjing University of Aeronautics and Astronautics (China) in 1997. He now is Ph. D. candidate in computer science at the Institute of Computing Technology, the Chinese

Academy of Sciences. His main research interests include VLSI/SOC test, ATE architecture design, and high performance processor design.

韩银和 ,1980 年生 ,博士 ,主要研究方向为 SOC 设计与测试、ATE 设计技术、处理器设计技术.

**Hu Yu**, born in 1975. Received her B. S., M. S. and Ph. D. degrees all in electrical engineering from the University of Electronic Science and Technology, Sichuan, China, in 1997, 1999 and 2003, respectively. She was a postdoctoral fellow in the Institute of

Computing Technology, the Chinese Academy of Sciences, Beijing, China, in 2005. She is presently associate professor there. Her main research interests include SOC design for testability, dependable computing, and EDA software design.

胡 瑜 ,1975 年生 ,博士后 ,副研究员 ,主要研究方向为 SOC 可测试性设计、可信计算和 EDA 软件设计.

Li Xiaowei, born in 1964. Ph. D. supervisor. Received his B. Eng. 's and M. Eng. 's degrees in computer science from Hefei University of Technology in 1985 and 1988 respectively, and his Ph. D. degree in computer science from the Institute of

Computing Technology , the Chinese Academy of Sciences in 1991. He worked with the Institute of Computer Technology , the Chinese Academy of Sciences as a professor in 2000. His main research interests include VLSI/SOC design verification and test generation , design for testability , low-power design , and dependable computing. He is a senior member of IEEE , and an associate editor-in-chief of the Journal of Computer-Aided Design and Computer Graphics (in Chinese).

李晓维 ,1964 年生 ,博士 ,研究员 ,博士生导师 ,IEEE 高级会员 ,主要研究方向为 VLSI/SoC 低功耗易测试设计、设计验证与测试、可信计算.

Zhang Yousheng, born in 1941. Received his B. Eng. 's degree in electronic science and technolog from Huazhong University of Science and Technology, and his Ph. D. degree in computer science from Leicester University in 1984. He works in Hefei

University of Technology as professor and Ph. D. supervisor. His main research interests include computer graphics, Image recognition and Understanding, Intelligent CAD.

张佑生,1941年生,教授,博士生导师,主要研究方向为智能CAD、计算机图形学、图像识别与理解等.

### Research Background

The system-on-chip (SOC) revolution has brought some new challenges to both design and test engineers. Among these challenges, power dissipation is one of the most important issues. Scan architecture represents the prevalent design for testability (DFT) in digital circuits testing. During test application in a scan-based circuit, power is dissipated in both the sequential scan elements and in the combinational logic. While scan vectors are loaded into a scan chain, the effect of scan-ripple propagates to the combinational logic and redundant switching occurs in the combinational gates during the entire vectors shifting period. Hence, low-power scan techniques should help to reduce power dissipation in the combinational logic. In this paper, we present an elegant signal blocking architecture, which is referred as PowerCut, to reduce power dissipation in the combinational logic during scan shifting. It breaks up the scan-ripple propagation between the combinational logic and the scan chain. This is achieved by inserting a transmission gate and a PMOS or NMOS transistor between the scan cell outputs and the combinational logic inputs, which essentially decreases the dynamic test power and let the circuit sleep into low leakage state. The proposed method is as effective as the other blocking methods and has little improvement in area or delay overhead during scan testing.