数据、人工智能等新型应用的兴起在集成度、访问速度等方面对存储器件提出了更高的要求.而随着半导体制造工艺的提升和器件尺寸的不断缩小,动态随机存储器(dynamic random access memory, DRAM)在制造成本、良品率和利润率方面面临着越来越大的挑战.此外,由于DRAM需要定期进行刷新操作,由此造成功耗提升和性能下降.在此背景下,新型非易失存储器(non-volatile memory, NVM)作为DRAM的可行替代技术受到了学术界和工业界越来越多的重视.与传统的DRAM相比,NVM器件具有集成度高、可扩展性高、静态功耗低、非易失等优点.

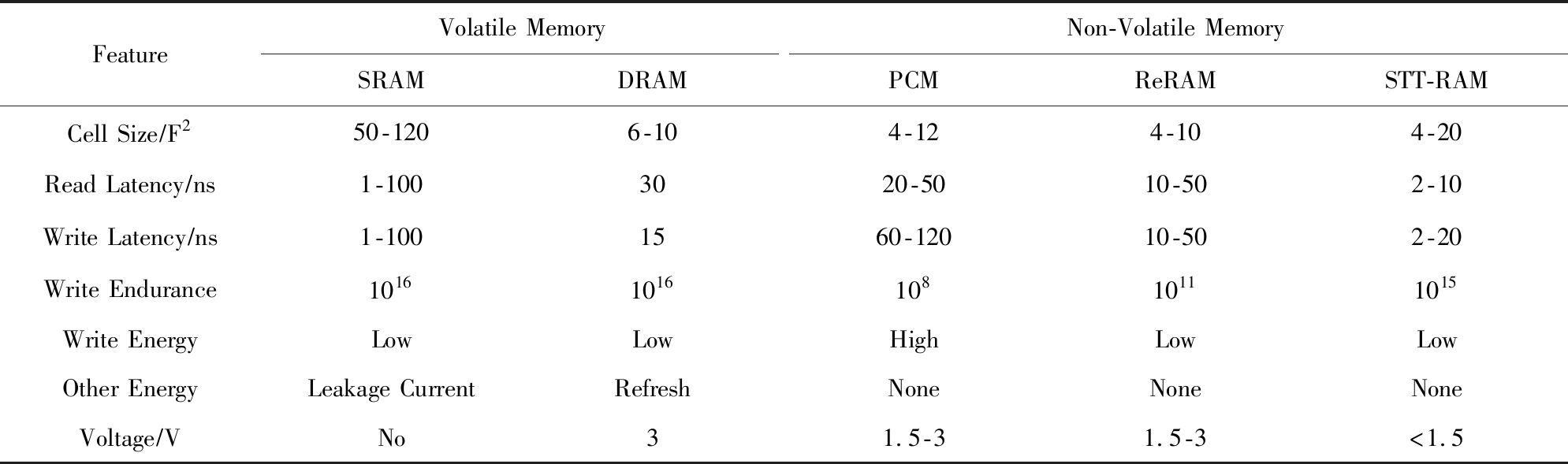

近年来,对NVM的研究主要集中于相变存储器(phase change memory, PCM)[1-2]、电阻式存储器(resistive RAM,ReRAM)[3]、自旋转移力矩存储器(spin-transfer toque RAM, STT-RAM)[4]等几种存储材料,并根据其不同的读/写操作速度替换现有层次化存储系统中相应的器件.其中PCM存储器利用硫系玻璃晶体在不同状态下表现出的不同电阻值保存信息,并通过脉冲电流实现可控的状态变化.电阻式存储器也称为忆阻器,通过在一个含有氧化物夹层结构的强相关电子材料两端施加不同大小和方向的电压改变其电阻值,并使用不同电阻值表示不同的逻辑值.STT-RAM则使用磁隧道结(magnetic tunnel junction, MTJ)保存数据,通过控制其自由层和参考层的相对磁力方向改变MTJ的电阻值,进而表示不同的逻辑值.3种非易失存储介质与传统易失存储介质的性能参数比较如表1所示:

Table 1 Comparison Across Different Storage Devices[5-6]

表1 存储介质参数对比[5-6]

FeatureVolatile MemoryNon-Volatile MemorySRAMDRAMPCMReRAMSTT-RAMCell Size∕F250-1206-104-124-104-20Read Latency∕ns1-1003020-5010-502-10Write Latency∕ns1-1001560-12010-502-20Write Endurance1016101610810111015Write EnergyLowLowHighLowLowOther EnergyLeakage CurrentRefreshNoneNoneNoneVoltage∕VNo31.5-31.5-3<1.5

从表1可以看出,与传统易失存储器相比,NVM存储器可以提供接近或更优的读访问性能,但在写访问延迟和写寿命方面存在较大差距.

目前,NVM器件正处在实用化的初始阶段,众多厂商纷纷推出了自己的解决方案:Intel和Micron公司在2016年底推出基于PCM的3D Xpoint Memory存储器[7],而HP和SanDisk则联合推出了基于ReRAM的SCM(storage class memory)存储器[8].但是,由于在寿命和写延迟方面仍存在很多问题,这些解决方案距离技术成熟尚有很大距离(例如与现有的SSD存储器相比,第1代3D Xpoint Memory的寿命仅提升了3倍[9]).

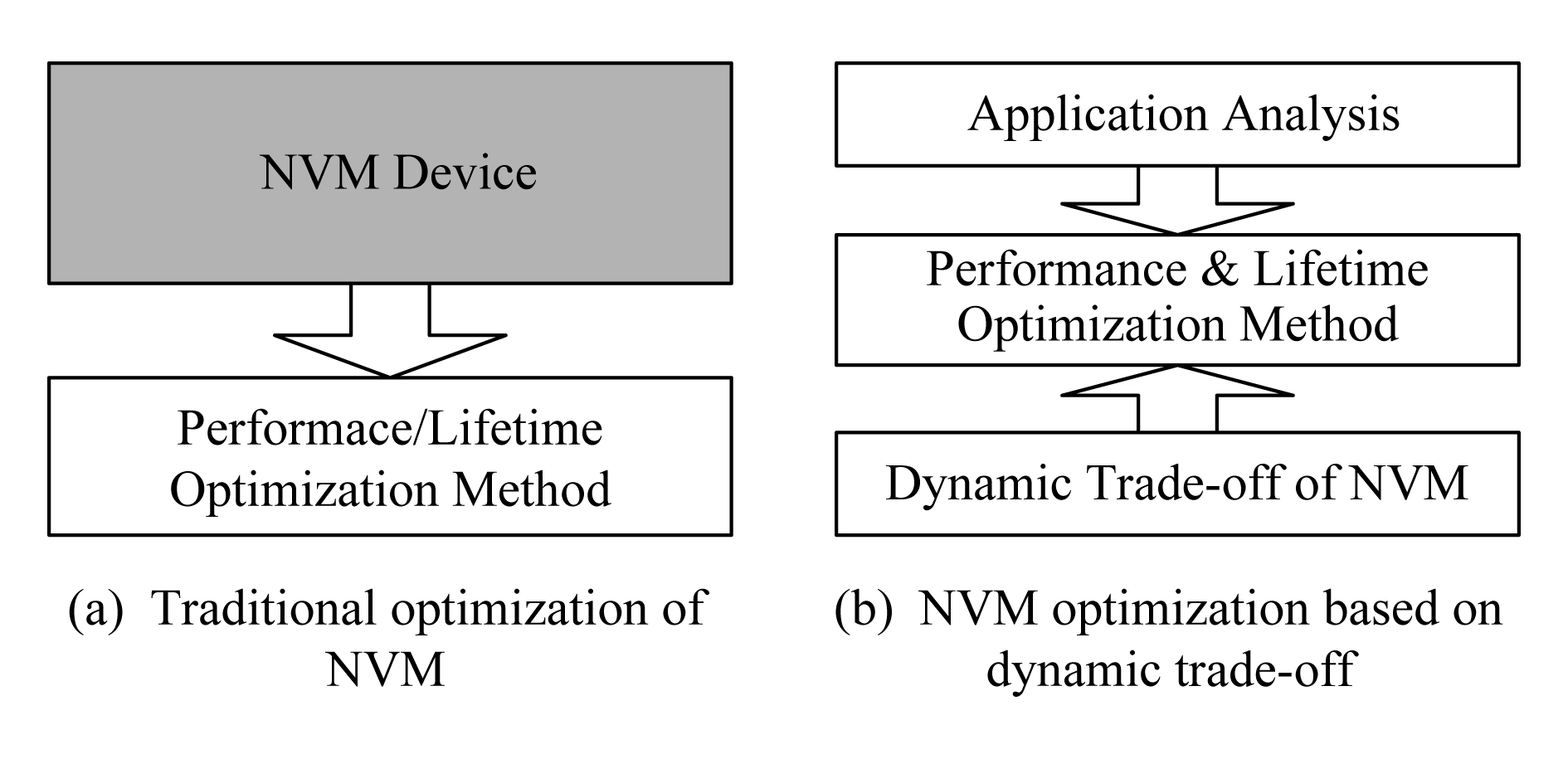

针对目前制约NVM大规模应用的问题,传统体系结构方法的思路是将NVM器件视为一个黑盒,通过在黑盒外围增加缓冲存储器和辅助控制电路,从而达到降低NVM存储器写延迟对系统性能的影响或延缓NVM存储器老化的目的(如图1(a)所示):

Fig. 1 Comparison of NVM optimization methods based on classical computer architecture method and dynamic trade-off

图1 基于传统方法和动态权衡特性的NVM优化比较

基于这一思路,研究人员提出了多种不同的解决方案:

1) 对于写延迟过大问题,一种主要的解决方案是通过提高写访问的并行度隐藏写延迟[10-12].除此以外,另一种常见思路是通过在NVM存储器的前端设置一个较大的缓存(如DRAM cache),将写请求存储在缓存后异步完成对NVM存储器的写访问[1-2].Qureshi等人[13]提出了一种新的思路,即当处在关键路径上的读请求到达且与正在执行的写操作冲突时,可以将正在执行的写操作暂停或终止,在读请求完成后继续或重新执行写操作,这种方法可以降低写延迟对于系统整体性能的影响.此外,Qureshi等人[13]通过对PCM存储器的SET和RESET操作的延迟分别进行分析,发现RESET操作延迟远小于SET操作,并基于这一发现提出了一种技术通过提前进行SET操作提升PCM存储器的写访问性能.

2) 对于NVM写操作寿命有限的问题,解决方案主要可以分为限制写操作和写分摊2种.其中限制写操作是指通过某种机制减少对NVM存储器的写操作从而延长设备的寿命,例如使用DRAM作为NVM存储器的缓冲[12].此外,Flip-N-Write技术利用被写入数据的特性减少写入数据时对NVM存储单元的擦写次数[10],以及Saadeldeen等人[14]提出在基于ReRAM的分支预测器中使用SRAM作为缓存的方案也都可以被归为这一类.写分摊技术是指通过将写操作分摊至全体NVM存储单元,减少由于写操作热点造成的部分存储单元过快老化,进而延长存储器整体寿命.其中,Start-Gap技术通过将写操作目标进行偏移,仅增加8 B的额外存储开销,可使存储器寿命达到理论寿命的95%[15].与此类似的解决方案还包括将cache line在内存页间进行偏移[2]、将bit在cache line内部进行偏移以及将cache line在段内进行偏移[16].

基于传统体系结构的方法虽然可以在一定程度上解决NVM存储器存在的问题,但同时也会带来一系列问题:

1) 需要增加一个或多个控制 电路对写访存请求进行分析、重定向等预处理操作,由于这些操作处于写访存请求执行的关键路径上,因此新增加的控制电路容易成为新的性能瓶颈.例如,在基于细粒度偏移[2,16]的写分摊技术中,由于需要为每一个写访存请求选择实际写入地址,因此在会造成写访存性能的降低.

2) 在对NVM存储器的性能或寿命进行优化的同时,往往会以牺牲其他指标作为代价.例如在通过减少写操作提升存储器寿命的方案中,为写访存请求选择新的目标地址将延长写访存操作的延迟[10];而在写暂停方法中,被中断的写操作在读访存请求完成后重新执行,这客观上增加了写操作的数量,使得存储器老化加快.

3) 造成控制逻辑更加复杂,不利于系统稳定.例如,在使用DRAM缓冲的性能或寿命优化方案中,需要特别的控制逻辑电路DRAM与NVM存储器的数据同步等操作.

由于实际系统对于存储器的性能和寿命同时具有较高的要求,因此上述基于传统体系结构方法的优化方案无法满足实际系统的需求.

近年来,随着对NVM存储材料的深入研究,人们发现在NVM存储材料中存在一些相互影响的参数,在其工作状态下,可以通过改变一个参数,使其他相关参数向着相反方向变化,这种特性被称为“动态权衡特性”[17-19].动态权衡特性为计算机体系结构研究提供了新的机遇,研究人员陆续提出了一系列基于NVM动态权衡特性的计算机体系结构优化方案[19-26].在此类设计方案中,NVM存储器不再被视为黑盒,而是基于其动态权衡特性,同时结合目标应用的特性,围绕这二者进行体系结构设计(如图1(b)所示).与传统的方案相比,基于动态权衡的解决方案在3个方面具有明显区别:

1) 在传统NVM研究中,器件特性在器件设计完成后就已确定,而动态权衡特性为体系结构设计者和系统级用户提供了影响器件特性的机会;

2) 在基于NVM动态权衡特性的体系结构研究中,研究者不仅需要考虑器件特性,还要综合考虑目标应用的特性,并为器件特性与目标应用特性寻找结合点;

3) 基于NVM动态权衡特性的体系结构设计中需要添加简单控制电路,以实现根据应用特性的变化动态调节NVM存储器的器件特性.

通过对动态权衡特性加以利用,基于NVM动态权衡特性的体系结构设计在很多方面具有明显的优势:1)与传统优化方案相比,此类方案仅需要少量或不需要额外存储开销;2)此类方法所需的辅助逻辑简单,由解决方案引入的额外延迟低;3)此类方法可在低硬件开销的前提下实现同时对多个目标进行协同优化;4)对系统整体性能影响小,避免了传统解决方案中由于对NVM某一方面进行优化而造成系统整体性能下降[20].

本文对NVM存储材料中存在的动态权衡特性进行了分析,包括存储密度与写延迟的关系、写延迟与写寿命的关系、写延迟与状态保持时间的关系.在此分析的基础上,本文对近年来基于这些动态权衡特性的NVM应用优化研究进行梳理.最后,本文还将对此类研究未来的发展做出展望.

1 NVM材料动态权衡特性

1.1 存储密度与访问延迟的关系

对于使用电阻值表示逻辑值的NVM材料(如ReRAM,PCM),可通过对其不同电阻值进行重新编码,实现在单一存储单元中存储多个逻辑状态.该技术被称为多层(multi-level cell, MLC)NVM,可用于提高存储密度或存储可靠性.对于MLC NVM而言,由于需要精确控制写入后存储单元的电阻值,因此MLC NVM的写操作通常采用基于多次迭代的模型[27].

在每个迭代中,需要将当前存储单元的电阻值读取并校验后再进行一次写操作,直至存储单元最终达到目标电阻值.因此,对于一个MLC NVM而言,写操作中迭代的次数随着NVM存储单元层数的增加而线性增长[27].文献[18]提出,MLC NVM存储单元的读延迟随该存储单元中存储层数的增加而呈指数增长.综上所述,MLC NVM写延迟与存储层数的关系可近似表示为

ReadLat(n)=![]() ReadLat(1)×ExpoBasen-1

ReadLat(1)×ExpoBasen-1![]() ,

,

WriteLat(n)=![]() (ReadLat(n)+WritePulseLat)×n

(ReadLat(n)+WritePulseLat)×n![]() ,

,

其中,ReadLat(n)表示当存储层数为n层时的读延迟,WritePulseLat表示每个迭代中写脉冲电流的持续时间.

1.2 写延迟与写寿命的关系

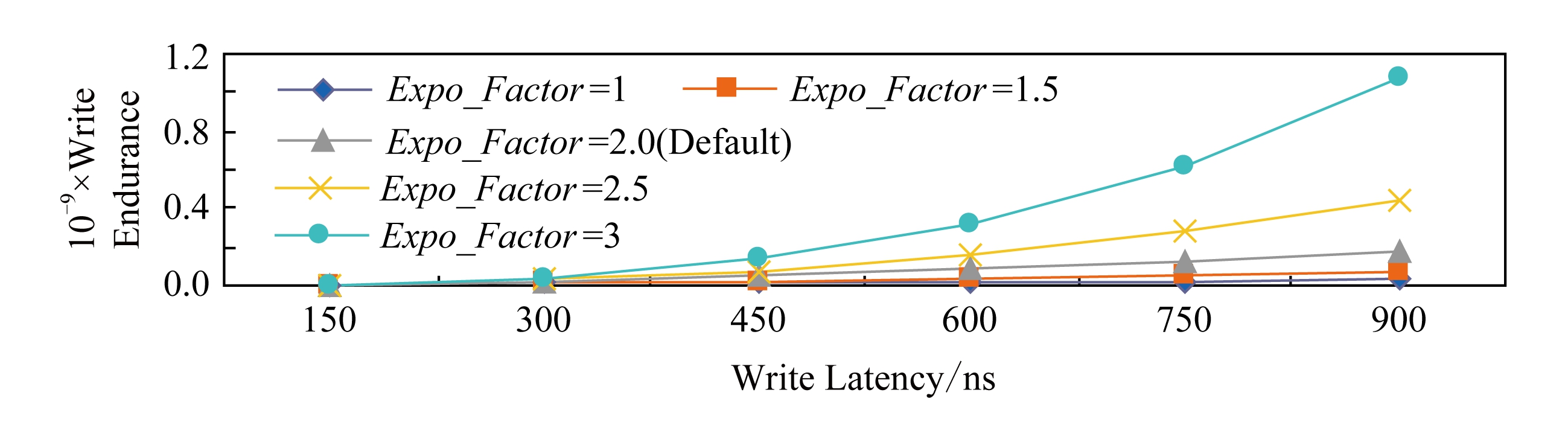

材料领域的相关研究工作表明,在多种NVM材料中,写延迟都与器件寿命存在相关关系[28-29].为了缩短写操作的延迟,往往需要在执行写操作时使用更多的能量[30-31],而过高的能量将加速器件的老化[29,32-33],进而导致器件寿命的降低.文献[17]以基于ReRAM的主存储器为应用场景,使用一个分析模型来定量描述NVM中写延迟与器件寿命的关系.根据该模型,NVM的寿命与写延迟之间的关系为

其中,tWP为写延迟,t0为器件相关常量,Expo_Factor为一个取值范围在1~3之间的器件结构相关常量.对于基于氧化金属层的器件而言[34],Expo_Factor的取值为2.0左右.当Expo_Factor=2.0时,器件的写寿命随写延迟增加而变化的情况如图2所示:

Fig. 2 The trade-off between write latency and write endurance of NVM device[20]

图2 NVM器件写延迟与写寿命之间的关系[20]

1.3 写延迟与状态保持时间的关系

在MLC PCM存储器中,由于制造工艺中存在的误差[35]、材料自身成分的波动[36]以及自身结构的细微变化[37],在擦写时电流、电压和持续时间相同,PCM存储器中不同单元阻值的变化情况也并不严格一致.因此,为了确保擦写的准确性,MLC PCM的写操作通常采用一种基于多次迭代的策略,每次迭代中包含一组“擦写-验证”操作.在每次写操作开始前,通常会使用一个RESET操作使得存储单元恢复到初始状态,随后采用多次“擦写-验证”操作直至存储单元的电阻值达到目标值.

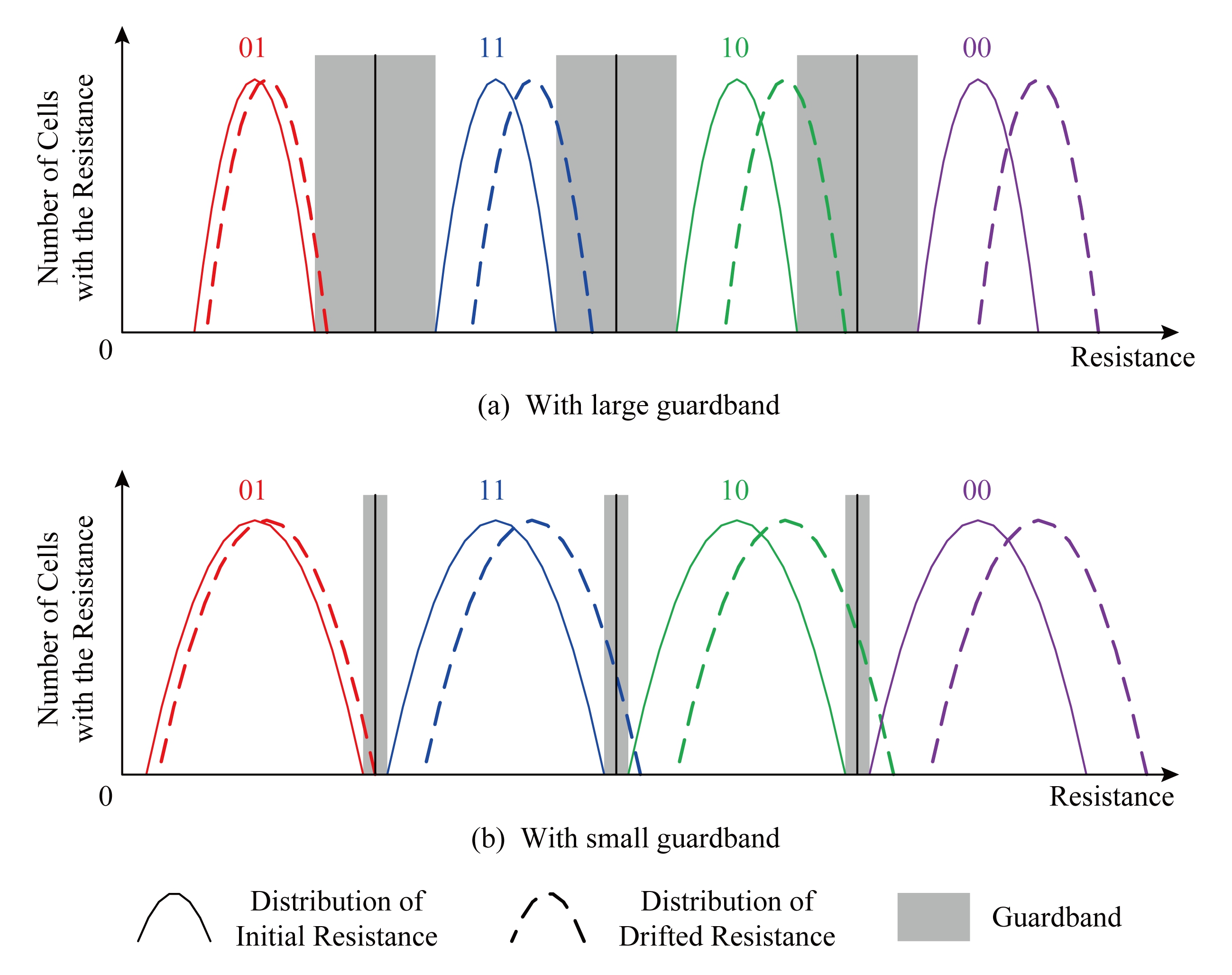

材料学研究发现,由于PCM晶体材料结构存在松弛性[38],其电阻值会自然增长,这种现象被称作“阻值漂移”[38].由于MLC PCM存储器使用不同的阻值域表示不同的逻辑值,因此当电阻值“离开”某一特定的阻值域时,其所代表的逻辑值可能会发生变化,这将使得MLC PCM不再具有非易失性.因此,为了克服阻值漂移对MLC PCM存储可靠性的影响,在定义阻值域时,通常在相邻的阻值域之间保留一个未定义的阻值区间用于隔离,这个阻值区间通常被称为“保护带”[39].图3描述了一个2 b MLC PCM存储单元,其整个阻值范围被分为4个阻值域(即“00”,“01”,“11”,“10”,采用格雷码规则排列).相关研究结果表明,阻值漂移的速度正比于存储单元中非晶相的体积分数.因此,对于一个MLC PCM存储单元,更宽的保护带将有助于容忍更多的阻值漂移,从而获得更长的数据保持时间.但是,保护带变宽将使得每个有效阻值域变窄,这对于写操作的准确性提出了更高的要求.为了保证写操作的准确性,写操作中每次迭代的阻值变化粒度将变小,整个写操作所需的迭代次数将增加,这将使得写操作需要消耗更多的能量(如图3(a)所示),但是由于其数据保持时间更长,因此很少需要刷新操作,器件的寿命更长.与之相反,当保护带变窄时,各个有效阻值域变宽,这使得写操作中可以使用粗粒度的迭代,减少写操作中迭代的数量,降低写操作所消耗的能量(如图3(b)所示),但由此会导致存储单元的数据保持时间更短.为了保证存储的正确性,存储器需要在存储单元状态失效之前进行刷新操作,这样会导致对存储器的写操作次数增加,器件寿命缩短.

Fig. 3 The problem of resistance drift in MLC PCM[21]

图3 PCM存储器“阻值漂移”现象示意图[21]

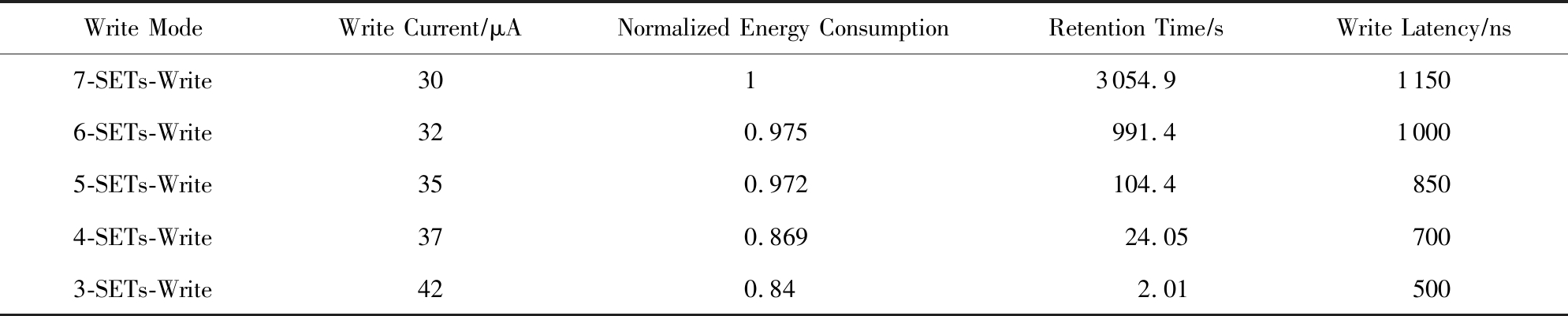

对于MLC PCM存储器而言,一个写操作包含一个RESET和多个SET操作.当保护带变宽时,有效阻值域变窄,此时SET操作的电流降低,需要的SET操作数量增长,存储单元的状态保持时间将相应地延长;相反,当保护带变窄时,有效阻值域变宽,此时SET操作的电流升高,需要的SET操作减少,存储单元的状态保持时间相应地缩短.为了定量描述这一动态权衡关系,文献[19]综合了多种不同角度的相关模型[38-41],提出了一种新的模型用于计算MLC PCM写延迟与状态保持时间的关系;在此基础上,文献[21]使用最新的基于20 nm工艺制程的参数[42],重新计算了相关数据,结果如表2所示.从表2可以看出,当写操作中SET操作的数量增多时,存储器可以采用更小的写电流完成写操作,存储单元的状态保持时间显著延长,但同时写操作的延迟增大,写访问性能降低;相反,若减少写操作中SET操作的数量,则写操作中需要使用更大的写电流,这样虽然可以缩短写操作延迟,但是存储单元的状态保持时间也会大幅缩短.

Table 2 Write Latency and Retention of Write Operations with Different Number of SET Iterations[21]

表2 包含不同数量SET的写操作中写延迟与状态保持时间的权衡关系[21]

Write ModeWrite Current∕μANormalized Energy ConsumptionRetention Time∕sWrite Latency∕ns7-SETs-Write3013054.911506-SETs-Write320.975991.410005-SETs-Write350.972104.48504-SETs-Write370.86924.057003-SETs-Write420.842.01500

在本节中,我们对NVM存储器中常见的动态权衡特性进行了介绍,这些特性为基于动态权衡特性的非易失存储器体系结构研究提供了物理基础.接下来,本文将对基于不同NVM动态权衡特性的体系结构优化研究进行分类梳理.

2 基于存储密度与写延迟关系的优化方法

由1.1节介绍可知,在ReRAM和PCM中,存储密度和读写延迟存在相关关系.在本节中,我们介绍了通过适当牺牲存储密度换取系统性能的优化方法.此外,在部分特定应用中,存储空间不足会带来明显的性能损失,因此在这些应用中可以通过适当延长写访问延迟而动态提升存储密度.这样虽然增大了写访存操作的延迟,但存储容量的提升依然可以使系统整体性能得到提升.

2.1 弹性存储

由于MLC NVM器件的读写延迟与存储密度存在相关性,因此在使用MLC NVM器件构建主存时需要在发挥其高存储密度优势的同时将各种负面影响降至最低.文献[25]分析了常见应用在运行时对内存的需求情况,发现不同应用在不同状态下对运行内存容量的需求存在很大波动,因此固定的内存容量难以满足不同应用的需求.基于这一分析结果,文献[25]提出了一种基于MLC PCM的可伸缩的弹性存储技术MMS.MMS将主存储器分为2个区域:运行于多层模式的“高存储密度-高访问延迟区域”和运行于单层模式的“低存储密度-低访问延迟区域”.MMS通过Memory Monitor对当前负载对内存的需求情况进行动态监测.当应用对于主存储器的需求增大时,运行于单层模式的存储区域比例会下降,一部分区域会变为多层模式以满足应用对内存容量的需求;当应用对主存储器容量的需求下降时,一部分多层模式的区域会切换为单层模式,通过牺牲存储容量换取系统整体性能的提升.实验结果表明,对于一个8 GB的MLC PCM主存储器而言,MMS可使用单层模式满足大部分访问请求的需要(95%的读请求和90%的写回请求),通过这种单层/多层模式的动态切换,包含MMS的系统可实现平均40%的性能提升.

类似地,文献[26]提出了一种名为AdaMS的技术,在电路层级实现了PCM存储单元在单层/多层模式之间的动态切换.基于这一技术,基于MLC PCM的固态硬盘可根据负载的需求情况在单层模式与多层模式之间进行切换,并配合专门的编制和运行时重映射技术,在负载较低时通过更多地采用单层模式提高固态硬盘的访问性能.实验结果表明:AdaMS可使得MLC PCM固态硬盘的吞吐率平均提升28%.

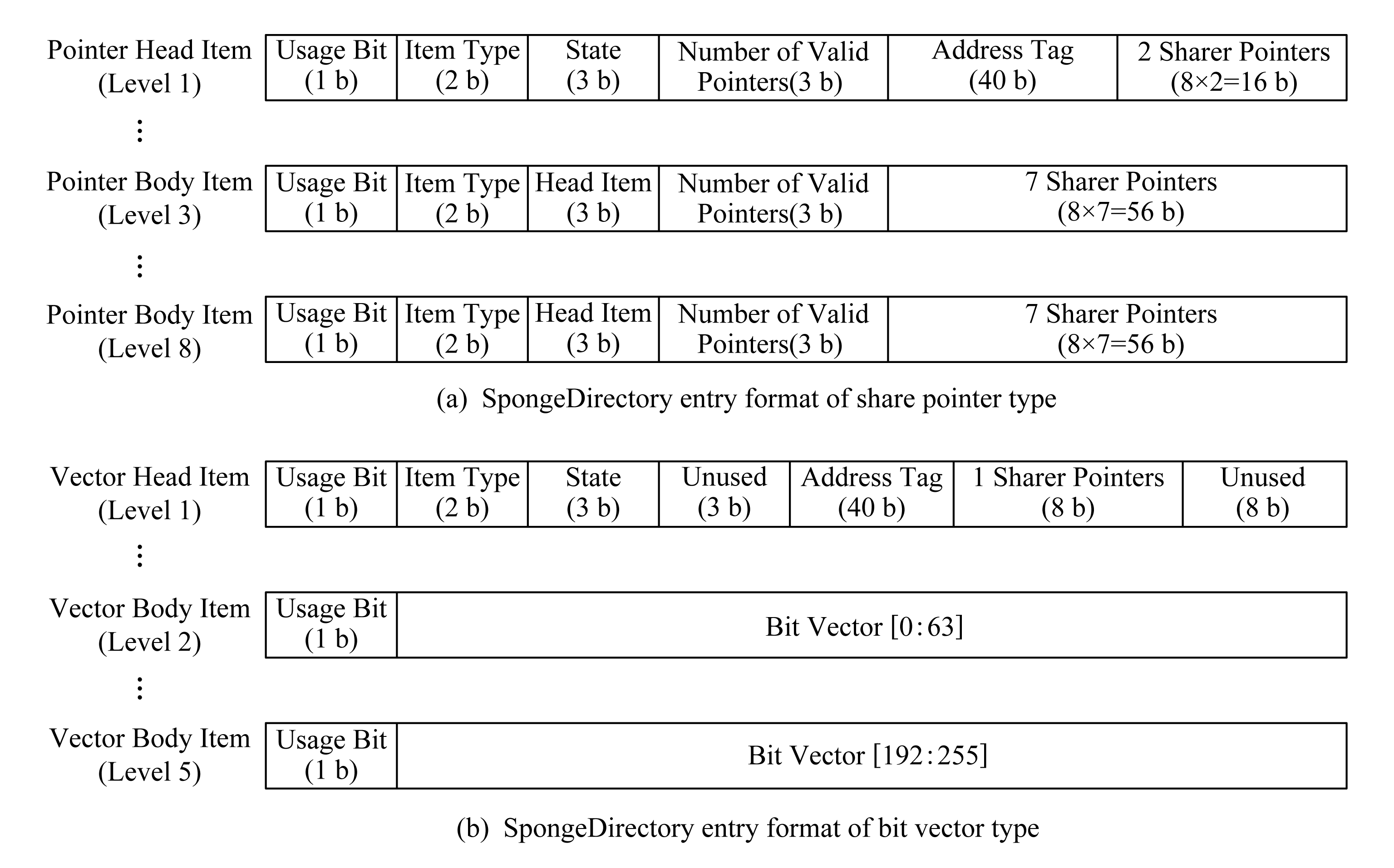

2.2 动态可伸缩目录表

基于cache一致性的共享存储对于多核/众核处理器芯片的可编程性具有重要意义.现有的多核/众核处理器普遍采用基于目录表的一致性协议.但是,随着处理器内部核数的增加,目录表所需的空间将呈超线性增加.因此,未来众核处理器设计中的一个重要问题是如何设计一种具有良好伸缩性的目录表结构.众多研究人员从降低目录表的能耗、延迟或复杂度等角度提出了多种不同的解决方案[43-46].但是,不同应用对于目录表的需求差异很大:在一部分应用中,要求目录表有较多的目录项,但大部分目录项中的共享信息较少;而另一部分应用中,则需要目录项数量较少,但多数目录项中的共享者数量较多.基于传统SRAM存储器很难设计出满足不同应用需求的弹性目录表[47-48].针对这一问题,文献[49]提出了一种基于多层ReRAM的目录表结构Sponge-Directory.SpongeDirectory通过将多个目录表条目保存在一个物理存储记录中,提升了目录表的存储密度,从而降低了目录表替换对于系统性能的影响.针对不同类型应用对于目录表的不同需求,Sponge-Directory提供了2种不同的逻辑存储格式,可根据应用的类型进行动态选择.如图4(a)所示,对于上述第1类应用,SpongeDirectory使用名为share pointer的存储格式,对应于同一内存区域的目录项被保存在同一物理记录中,其中地址信息被保存在该物理记录的第0层,后续每条目录项被依次保存在该屋里记录的更高层;而对于上述第2类应用,则使用名为bit vector的存储格式(如图4(b)所示),物理记录的第0层保存目录项地址信息,物理记录的高层保存共享者信息,其中每位对应于一个共享者.

Fig. 4 The entry formats of SpongeDirectory[49]

图4 SpongeDirectory结构示意图[49]

在采用SpongeDirectory的系统中,尽管使用的多层ReRAM存储器延长了目录表的读写延迟,但由于其提升了存储密度和目录表使用效率,降低了由于目录表替换造成的性能损失,因此系统性能和电路面积依然得到了明显的优化.实验结果表明:与传统目录表相比,SpongeDirectory在性能近似的前提下,可将存储单元数量缩减至1/18,同时将能耗缩减至1/8.

2.3 基于弹性存储的Hash Table算法优化

在很多算法和应用中,Hash Table都是一种重要的数据结构.随着应用和数据规模的增长,实现高效的Hash Table结构的重要性和难度也在日益提高.传统的Hash Table通常基于链表实现,Hash Table中各项的地址动态可变并在内存中随机分布.这种实现方式虽然可以提高内存使用效率,但是却影响了预取(prefetching)的效果并降低了指令级并行度.针对这一问题,文献[24]提出了一种基于MLC PCM的可扩容Hash Table技术Herniated Hash Table.该技术可根据应用的需要,通过动态增加PCM单元同一电阻域中存储的位数实现将多个相邻的Hash Table记录保存在同一个物理地址的不同层中,以便于读取连续的Hash Table记录.当该物理地址的存储层数达到上限时,链表会指向其他物理地址并继续使用不同层存储连续的Hash Table记录.Herniated Hash Table虽然会使Hash Table记录的读写延迟增大,但是通过配合专门设计的编址和预取机制,该技术依然可以通过提高访问并行度达到提升性能的目的.实验结果表明:与基于单层PCM主存储器的链表式Hash Table结构相比,Herniated Hash Table在使用4层PCM的情况下可实现4.8倍的存储密度提升以及67%的性能提升.

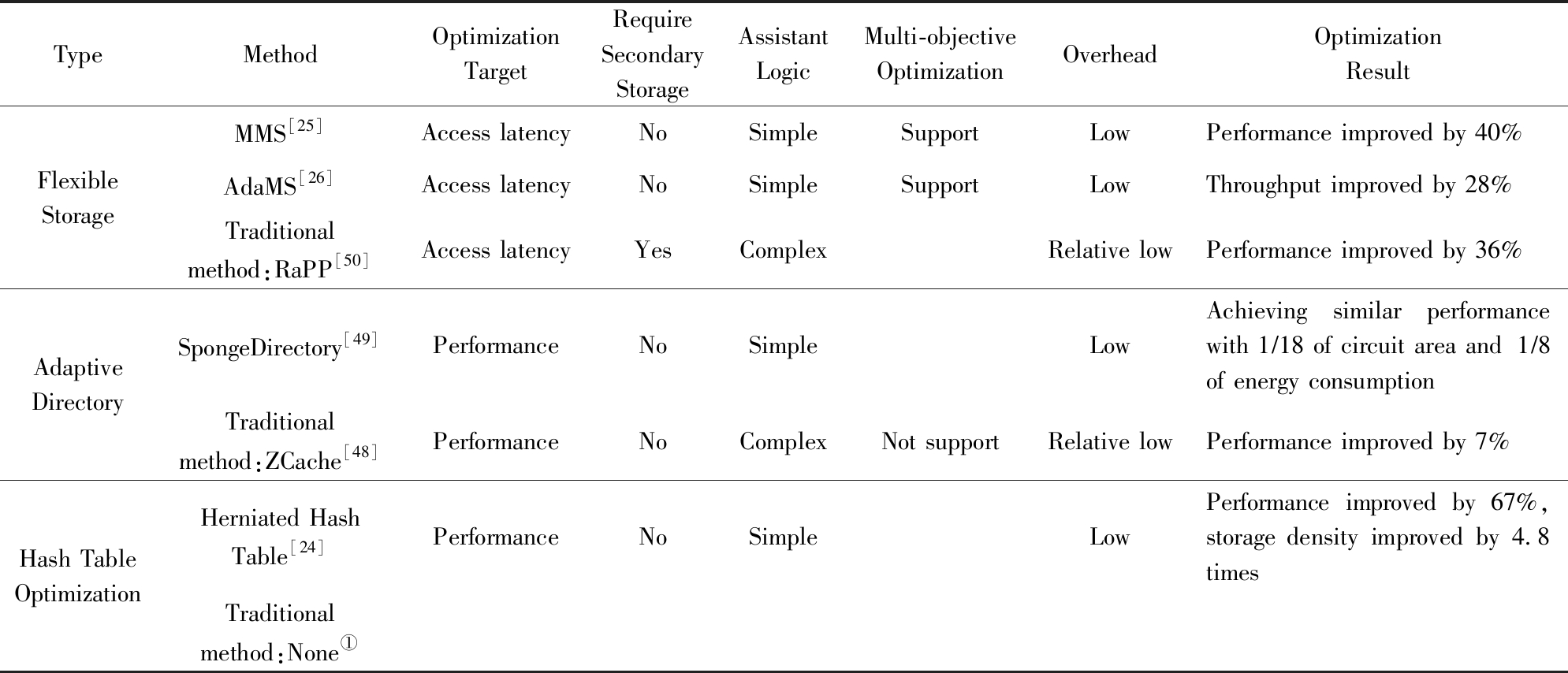

2.4 小 结

表3列举了本节所介绍的基于“存储密度-访问延迟动态权衡特性”的相关优化工作,并将其与基于传统体系结构方法的相关工作进行了对比.从中我们可以看出,与传统体系结构方法相比,基于动态权衡特性的性能优化方法在硬件开销、简化控制逻辑等方面具有明显的优势.

Table 3 Qualitative Comparison of Optimization Using the Storage Density vs Access Latency Trade-off

表3 基于“存储密度-访问延迟动态权衡特性”的相关优化工作比较

TypeMethodOptimizationTargetRequire SecondaryStorageAssistantLogicMulti-objectiveOptimizationOverheadOptimizationResultFlexibleStorageMMS[25]Access latencyNoSimpleSupportLowPerformance improved by 40%AdaMS[26]Access latencyNoSimpleSupportLowThroughput improved by 28%Traditional method:RaPP[50]Access latencyYesComplexRelative lowPerformance improved by 36%AdaptiveDirectorySpongeDirectory[49]PerformanceNoSimpleLowAchieving similar performance with 1∕18 of circuit area and 1∕8 of energy consumptionTraditional method:ZCache[48]PerformanceNoComplexNot supportRelative lowPerformance improved by 7%Hash TableOptimizationHerniated HashTable[24]PerformanceNoSimpleLowPerformance improved by 67%,storage density improved by 4.8 timesTraditionalmethod:None①

① To our best of knowledge, all the existing Hash table optimization is based on software, and there is no similar work to compare.

Fig. 5 Bank-Aware Mellow Write scheme[20]

图5 Bank-Aware Mellow Write写策略[20]

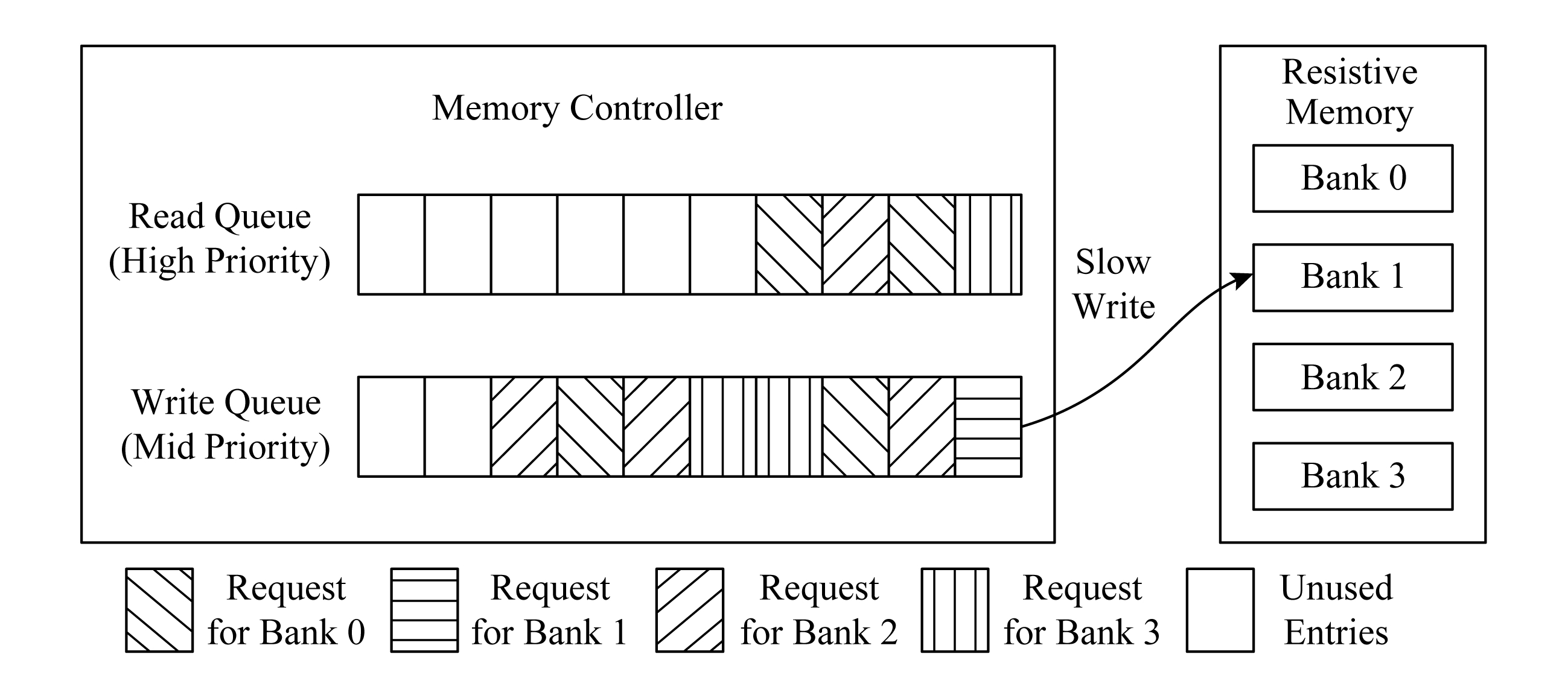

3 基于写延迟与写寿命关系的优化方法

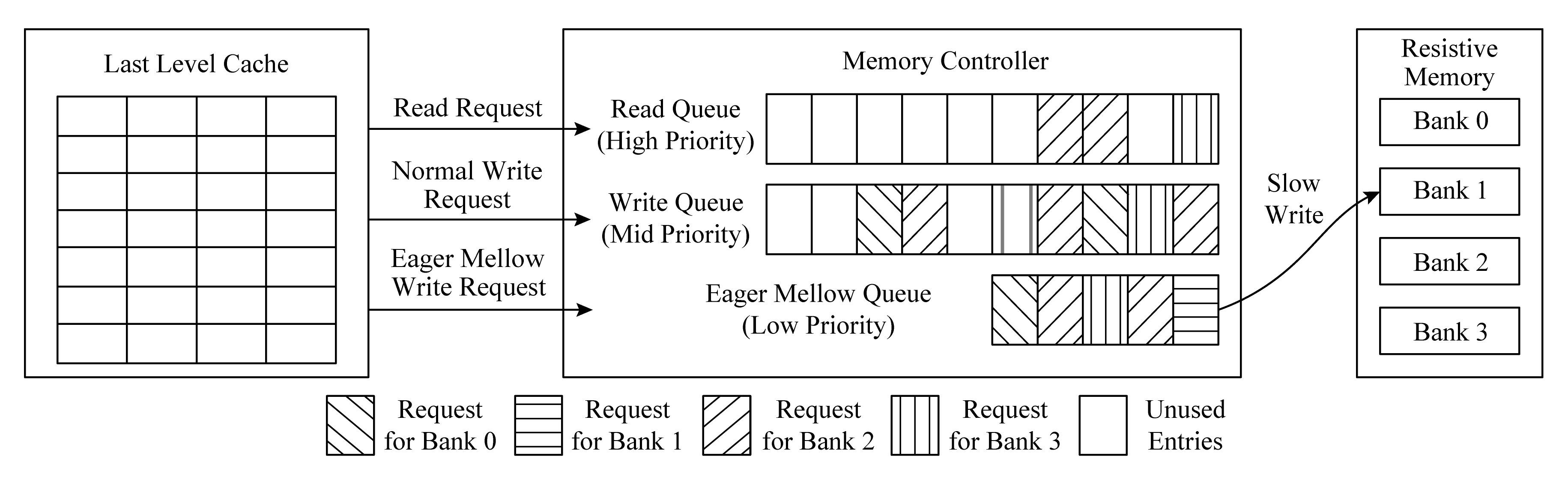

由1.2节介绍可知,对于NVM材料而言,写延迟和写寿命存在相关性.基于这一动态权衡关系,文献[20]提出了一种名为Mellow Write的技术,在尽量减少额外硬件开销的前提下提升NVM存储器的寿命.与原有基于写分摊和减少写操作的思路不同,Mellow Write主要通过延长写操作延迟(“慢写”)减少单次写操作对NVM存储单元的磨损程度,从而实现延长存储器寿命的目标.

为了减少写延迟延长对系统性能的影响,Mellow Write包含了2种策略:Bank-Aware Mellow Write和Eager Mellow Write.如图5所示,在Bank-Aware Mellow Write策略中,通过扫描写访存队列中的写请求,当一个bank只有一个写请求时,该请求会采用慢写的方式完成.为了进一步提升Mellow Write的性能,在Eager Mellow Write策略中(如图6所示),通过对末级缓存(last level cache, LLC)进行扫描,挑选无用的“脏数据”并将其主动地采用慢写的方式进行写回.同时,在内存控制器中增加了专门的Eager Mellow Queue用于主动生成的慢写请求.

为了进一步提升NVM存储器的寿命,Mellow Write中还包含一种名为Wear Quota的技术:将程序运行的整个过程划分为一些列固定时长的采样区间,在每个采样区间中计算区间内写操作对主存造成的累计磨损情况,当累计磨损超过一定阈值时,在下一个采样区间内将只采用慢写模式完成所有写请求.

Fig. 6 A high level view of a processor and a memory controller using Eager Mellow Write[20]

图6 采用Eager Mellow Write策略的系统结构图[20]

Mellow Write中的一些参数取值与应用特征相互作用将会对系统性能造成很大影响.为了使系统始终运行于最优状态,Mellow Write需要针对不同应用特征动态调节自身参数.但是,由于参数的数量众多,通过建模实现自身参数的求解变得十分困难.针对这一问题,文献[51]提出了一种基于机器学习的参数动态选择技术.该技术通过在程序运行时对处理器各项状态参数及程序行为特征进行周期性采样,在线训练一个机器学习模型,同时使用该模型为下一个采样周期选择适当的系统配置参数.实验结果表明:该方法可以在最小化动态能耗的同时,使性能与理论最优值的差距缩小到5%以内.

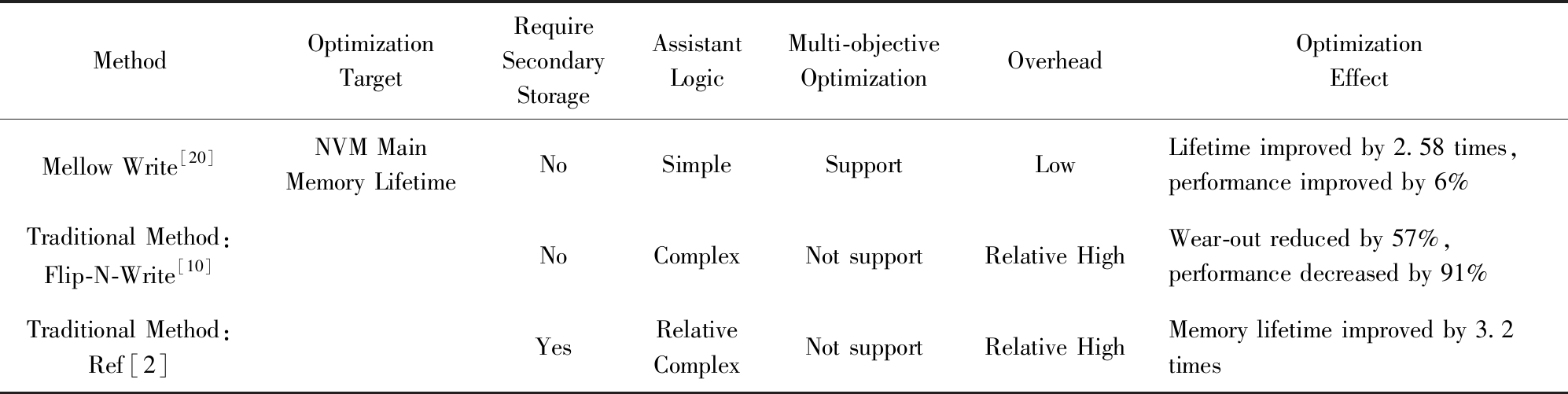

表4将基于“访问延迟-写寿命动态权衡特性”的NVM存储器优化与基于传统体系结构方法的NVM存储器优化进行了比较.从表4可以看出,由于Mellow Write不需要对写访存请求进行细粒度分析,因此需要的辅助逻辑和额外开销都很小;同时,Mellow Write通过为写访存请求选择适当写模式的方式对器件寿命和系统性能进行平衡,避免了引入缓冲存储器以及由此带来的控制逻辑复杂化的问题.此外,Mellow Write避免了在优化存储器寿命的同时对系统性能造成影响,实现了多目标协同优化.

Table 4 Qualitative Comparison of Optimization Using the Access Latency vs Endurance Trade-off

表4 基于“访问延迟-写寿命动态权衡特性”的相关优化工作比较

MethodOptimizationTargetRequireSecondaryStorageAssistantLogicMulti-objectiveOptimizationOverheadOptimizationEffectMellow Write[20]NVM MainMemory LifetimeNoSimpleSupportLowLifetime improved by 2.58 times,performance improved by 6%Traditional Method:Flip-N-Write[10]NoComplexNot supportRelative HighWear-out reduced by 57%,performance decreased by 91%Traditional Method:Ref[2]YesRelativeComplexNot supportRelative HighMemory lifetime improved by 3.2 times

4 基于写延迟与状态保持时间关系的优化方法

由1.3节介绍可知,在MLC PCM中存在着写延迟与状态保持时间之间的动态权衡关系.同时,由于不同延迟的写模式对于写电流的需求不同,因此写延迟不同也会导致写功耗的变化.此外,对于基于MLC PCM的主存储器而言,为了保证数据的正确性,在其状态保持时间结束前需要进行刷新操作,由此引入的额外写操作也会加速存储单元的老化.因此,写延迟与状态保持时间之间动态权衡关系也可以很容易地扩展为包含写延迟、写功耗、状态保持时间、器件寿命在内的多方之间的动态权衡关系.这为体系结构设计提供了充足的空间.本节将对基于这一动态权衡关系的体系结构设计方法进行介绍.

4.1 嵌入式系统主存储器

由于MLC PCM具有写延迟大、静态功耗低的特点,因此非常适合作为RAM和FLASH的替代品,应用于对写性能要求不高但要求低功耗的嵌入式设备中.针对嵌入式系统的特点,研究人员提出了一系列基于存储器动态权衡特性的优化方案.

文献[19]针对嵌入式系统中应用程序的访存特点,提出了一种名为CDDW的技术.该技术通过在编译阶段对代码中的写操作指令进行静态扫描,估算出数据在最坏情况下的生命周期长度.基于这一估算结果,编译器将为该数据选择最适合的写模式.通过该方法,CDDW可使基于MLC PCM的存储器在性能和写延迟之间达到更优的平衡.实验结果表明,CDDW可使得系统性能提升6.3%,同时将写能耗降低32.4%.

在CDDW的基础上,文献[22]通过分析发现,对于嵌入式应用中大量存在的循环模块,由于其中数据的生命周期非常长,因此对这些数据采用长延迟写操作将对系统性能和能耗带来很大影响.基于这一分析,文献[22]提出了一种名为WMALT的循环感知技术.该技术通过在编译阶段对代码的扫描,发现处于循环模块中的数据项,并采用低延迟写操作去改写这些数据项.实验结果表明:当WMALT与CDDW技术配合使用时,相比于单纯使用CDDW的情况下可实现50.8%的性能提升,同时降低32.0%的动态能耗.

Fig. 7 A high level overview of RRM and its relationship to the LLC and memory controller[21]

图7 RRM结构概述及其与LLC和内存控制器的关系[21]

文献[23]针对嵌入式处理器中基于MLC PCM的SPM存储器,提出了一种名为MMAS的算法.该算法使用整数线性规划方法为写操作指令和数据项寻找近似最优的调度方案,从而达到缩短数据项生命周期并更多地使用低延迟写操作的目的.MMAS可在多项式时间内为大型程序寻找到近似最优的调度结果.实验结果表明,MMAS算法可使访存时间平均缩短38.79%.

4.2 通用计算系统主存储器

除了嵌入式系统,MLC PCM也可作为主存储器被应用于高性能通用计算系统中.相比于嵌入式系统,通用计算系统的存储结构和应用更加复杂,这使得为嵌入式系统设计的MLC PCM优化方法不适用于通用计算系统,这种不适应主要体现在3个方面:

1) 应用于嵌入式系统的这些方法只适用于能够在编译阶段进行分析的静态应用,而无法适用于动态应用;

2) 由于cache的过滤效应,原有方法难以应用在基于cache的系统上,这是因为cache使得对MLC PCM存储器的读/写操作分布与应用中产生的读/写请求分布不同;

3) 操作系统对内存的管理会使得实际的访存行为特征与基于静态分析做出的预测结果更加不同.由于cache和操作系统在通用计算系统中都是不可或缺的组成部分,同时通用计算系统上所运行的程序多为动态应用,因此,这类基于静态分析的方法难以应用在通用计算系统上.

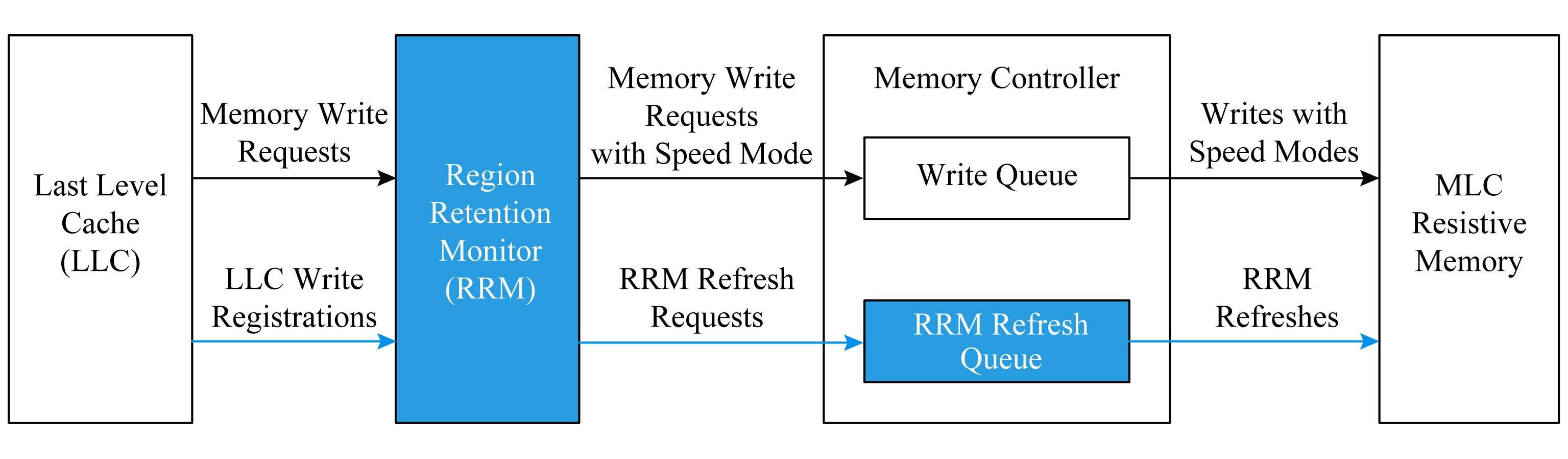

针对这些问题,文献[21]提出了一种名为RRM的新型解决方案,实现了MLC PCM主存储器性能与寿命的平衡提升.文献[21]首先分析了典型应用在运行时写访存请求的分布情况,发现在典型应用中绝大多数写请求集中于少数内存区域中.文献[21]将这类内存区域称为写访存热点区域(hot-written memory region),其余区域为写访存非热点区域(cold-written memory region).在RRM中,包含2种写操作:1)采用较多迭代周期、弱电流的长保持时间写操作(long retention write),简称LR写;2)采用较少迭代周期、强电流的短保持时间写操作(short retention write),简称SR写.对于采用SR写的存储单元,由于其状态保持时间较短,需要定期对其进行刷新操作.RRM对写访存热点区域采用SR写操作,对非热点区域则采用LR写操作,由于大部分的写请求使用低延迟的SR写操作完成,内存系统的性能与只采用LR写操作的系统相比将得到很大的提升.同时,由于热写区域相对较少,因此与全部采用SR写操作的系统相比,该系统中的刷新操作显著减少,同时内存的寿命也会得到提升.

RRM的系统结构如图7所示,RRM位于末级高速缓存(LLC)和内存控制器(memory controller,MC)之间.RRM将记录写操作的目标地址,并根据这些记录预测当前写操作的目标地址是否属于热写区域.对于写访问热点区域,将采用SR写操作,而对于其他区域则采用LR写操作.此外,为了保证数据正确性,RRM将定期对部分内存区域发送刷新请求.当热写区域变为冷写区域时,RRM将使用LR写操作刷新之前的写访存热点区域.由于使用了动态写模式选择技术,RRM平衡了MLC PCM存储器的性能与寿命.需要说明的是,由于RRM只记录热写区域信息,因此RRM所需要的存储开销非常有限.实验结果表明,与LR写静态策略相比,RRM可使系统性能平均提升62.0%,同时寿命可达到LR写静态策略的60%.

与RRM不同,文献[52]通过对典型应用写访存请求的时间分布特征进行分析,发现典型应用中写访存请求的时间分布具有明显的不均匀性.基于这一特性,文献[52]提出了一种名为QnD的轻量级的写访存性能优化方案.该方案通过对内存控制器中写访存队列的负载进行感知,当系统中写访存请求较多时,动态选择使用SR写模式完成写请求,然后在目标地址状态保持时间结束之前使用LR写模式对其进行刷新;而在系统中写访存请求较少时,则直接使用LR写模式完成写请求.通过这样的写模式选择机制,QnD使用极低的硬件开销实现了MLC PCM主存储器的性能提升,同时存储器寿命并未大幅下降.实验结果表明,QnD可实现30.9%的性能提升,同时存储器寿命达到7.58年.

4.3 其他存储设备

除了主存储器之外,MLC PCM也被用作文件缓冲器等其他存储设备.对于这类存储设备,结合其应用特征,依然可以利用写延迟与状态保持时间的关系进行优化.

文献[53]提出了一种名为Amnesic Cache的基于MLC PCM的文件缓存,该缓存工作于LLC与SSD/硬盘之间.Amnesic Cache的主要目标是降低对MLC PCM的访问延迟,其首先使用低延迟写操作执行所有写请求,然后使用长延迟写操作进行刷新,以此换取较长的状态保持时间.但是,Amnesic Cache不适用于基于MLC PCM主存的通用计算系统:首先,Amnesic Cache需要较大的辅助存储器配合工作,因为其需要记录每一个写操作的信息以便在其失效前进行刷新;其次,在执行每一个写请求时,Amnesic Cache都需要对于一个存储区块进行多次写操作,这将使得存储器寿命降低.Amnesic Cache作为文件缓存可以与SSD和主存很好地配合工作,这是由于其写操作并不频繁,因而对器件寿命的要求并不高.但是,这项技术却不适用于通用计算系统的主存储器.与Amnesic Cache类似,文献[54]提出了基于“低延迟-低状态保持时间写操作”的MLC NAND Flash加速技术,由于这项技术也需要复杂的硬件结构和机制用于对状态保持时间做出追踪,因此这项技术也很难被用于主存储器中.

文献[54]提出了一种名为NVM Duet的技术,该技术为主存和外部存储提供了一种统一的存储架构.在NVM Duet中,PCM可被用于主存或外部存储器件,当PCM作为主存使用时,NVM Duet为其使用“低延迟-低状态保持时间”写模式;而当PCM作为外部存储器时,NVM Duet为其选用“长延迟-长状态保持时间”写模式.但是,对于一个应用模式,NVM Duet只能采用一种写模式.而对于主存而言,访问行为的特征是时刻变化的,因此NVM Duet的技术并不适用于主存.此外,由于NVM Duet需要操作系统的支持,因此也难以在目前主流的商用操作系统中得到应用.

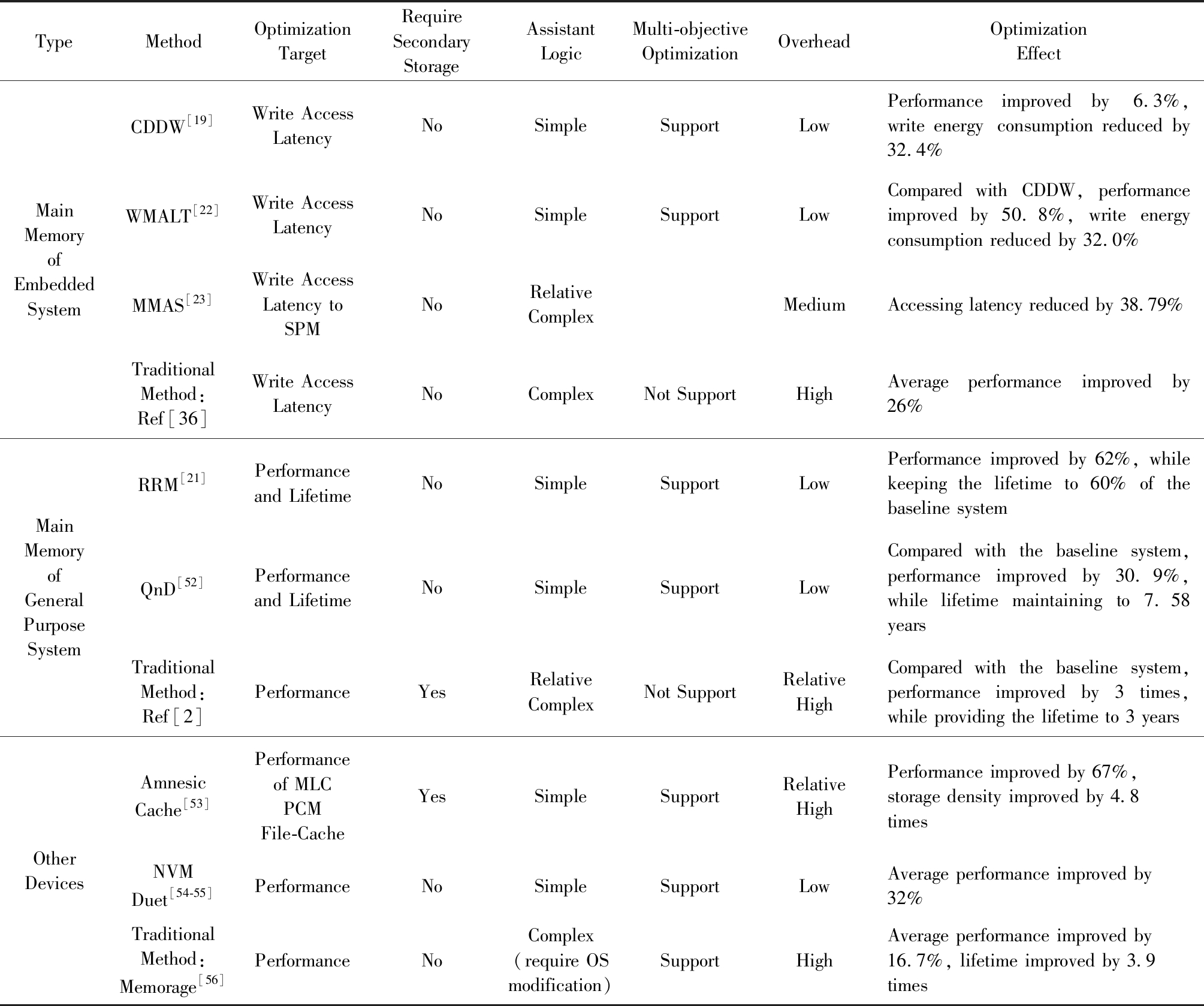

4.4 小 结

表5列举了本节所介绍的基于“写访问延迟-状态保持时间动态权衡特性”的相关优化工作,并将其与应用传统体系结构方法的相关工作进行了简要比较.从表5可以看出,尽管基于传统体系结构方法的优化工作可在性能或寿命方面取得显著效果(如文献[2]),但是采用动态权衡特性的工作可同时对多个目标提供优化,从而更好地满足实际系统的需求.此外,绝大多数基于动态权衡特性的优化工作不需要辅助存储,同时避免了使用复杂的控制逻辑和修改操作系统,这也使得基于动态权衡特性的优化工作更容易被实际系统所使用.

5 总结与展望

处理器性能的提升对存储系统的访问速度和能效提出了更高的要求.然而,现有存储系统无法满足高性能计算的需求,成为了提升系统整体性能和能效比的瓶颈.在这一背景下,新型非易失存储器件的出现为提高存储系统的能效比提供了新的选择.近年来,学术界和工业界开始尝试使用新型非易失存储器件替代原有的存储器件.但是,这种做法面临着诸多问题.首先,新型非易失存储器件存在诸多与传统存储器件不同的电气特性,如读写延迟不对称、写寿命有限等,这使得直接使用这类器件替换原有存储器件的方法无法发挥其优势;其次,现有的软件系统都是基于原有存储器件特性进行开发的,其算法和数据结构的设计也是基于原有器件进行优化,这些算法不能很好地适用于新的存储器件;最后,新型存储器件的引入给系统设计带来了新的问题.

Table 5 Qualitative Comparison of Optimization Using the Write Latency vs. Retention Time Trade-off

表5 基于“写访问延迟-状态保持时间动态权衡特性”的相关优化工作比较

TypeMethodOptimizationTargetRequireSecondaryStorageAssistantLogicMulti-objectiveOptimizationOverheadOptimization EffectMainMemoryofEmbeddedSystemCDDW[19]Write AccessLatencyNoSimpleSupportLowPerformance improved by 6.3%, write energy consumption reduced by 32.4%WMALT[22]Write AccessLatencyNoSimpleSupportLowCompared with CDDW, performance improved by 50.8%, write energy consumption reduced by 32.0%MMAS[23]Write AccessLatency toSPMNoRelativeComplexMediumAccessing latency reduced by 38.79%TraditionalMethod:Ref[36]Write AccessLatencyNoComplexNot SupportHighAverage performance improved by 26%Main MemoryofGeneralPurposeSystemRRM[21]Performance and LifetimeNoSimpleSupportLowPerformance improved by 62%, while keeping the lifetime to 60% of the baseline systemQnD[52]Performance and LifetimeNoSimpleSupportLowCompared with the baseline system, performance improved by 30.9%, while lifetime maintaining to 7.58 yearsTraditionalMethod:Ref[2]PerformanceYesRelative ComplexNot SupportRelative HighCompared with the baseline system, performance improved by 3 times, while providing the lifetime to 3 yearsOtherDevicesAmnesicCache[53]Performance of MLCPCMFile-CacheYesSimpleSupportRelativeHighPerformance improved by 67%, storage density improved by 4.8 timesNVM Duet[54-55]PerformanceNoSimpleSupportLowAverage performance improved by 32%TraditionalMethod:Memorage[56]PerformanceNoComplex(require OSmodification)SupportHighAverage performance improved by 16.7%, lifetime improved by 3.9 times

长期以来,计算机硬件性能的提升来源于器件领域和计算机体系结构领域共同的努力.这种合作通常表现为2种形式:1)器件领域更关注器件的静态特性(如读/写延迟、寿命等),而体系结构领域则致力于调整计算机的硬件结构,使其能够更好地适应器件的特性;2)体系结构工程师将对于器件的需求提交给器件工程师,而器件工程师则会调整器件的结构和参数以满足特定系统的需求.但是,由于之前的研究中往往追求“完美”的器件(如兼具更短的读/写延迟和更长的寿命),NVM器件中不同参数间存在的动态权衡关系并没有得到器件领域足够的重视,因此体系结构领域也并没有充分利用这些动态特性.

本文对近年来基于NVM器件自身动态权衡特性的体系结构研究工作进行了梳理.通过梳理我们发现,这类工作通常包含4个步骤:1)器件和材料研究人员发现并归纳出NVM器件中所包含的动态权衡特性;2)计算机体系结构设计人员对目标应用对NVM存储器的访问特征进行分析,包括访存请求的空间分布、时间分布等;3)在此基础上,体系结构设计人员为NVM存储器动态权衡特性和目标应用访存特征寻找结合点,以探索利用NVM动态权衡特性对系统进行优化的可能性;4)根据前述3个分析结果,体系结构设计人员在处理器中加入应用特性感知电路以及动态权衡调节信号生成电路,以便利用NVM存储器的动态权衡特性为应用所表现出的不同访存特征动态选择适当的NVM存储器参数或工作状态.通过上述分析和设计过程,基于NVM存储器动态权衡特性的体系结构设计可以实现同时对多个目标进行优化的目的,例如在RRM技术中[21],通过对MLC PCM存储器中写延迟与状态保持时间之间的动态权衡关系加以利用,为写访存热点区域和非热点区域选择不同的写模式,RRM实现了系统性能与NVM存储器寿命的平衡优化,在性能提升62.0%的同时使存储器寿命达到了理论最优值的60%.

对于基于NVM存储器动态权衡特性的体系结构优化研究工作,我们认为在4个方面仍存在着机遇与挑战:

1) 物理学和器件领域研究的不断发展,为体系结构研究提供了新的机遇.一方面,随着新型存储材料的应用,相关体系结构设计过程中需要考虑新器件中不同于传统器件的特性;另一方面,随着对现有NVM材料研究的深入,新的动态权衡关系不断被发现.如何利用这些新材料和新的动态权衡关系进行计算机体系结构层面的优化设计,将是一个非常具有挑战性的问题.

2) 现有的研究工作大多是利用器件的一项动态权衡关系进行优化设计,但是在真实的器件中往往同时存在多个动态权衡关系.因此,如何同时利用多个动态权衡关系进行优化设计是一个值得关注的研究方向.

3) 在利用动态权衡关系进行优化设计的过程中,往往需要引入新的辅助结构,这增加了系统中参数的数量;同时,系统中原有参数的选择也会对新引入的辅助结构的性能造成影响.这些问题使得原有芯片设计中的经验参数无法满足新的系统设计需要.因此,如何针对基于器件动态权衡关系的设计,在更大的设计空间内探索优化的参数组合,将是体系结构研究人员和设计人员需要面对的重要问题.

4) 基于器件动态权衡特性进行系统结构设计依赖于对应用行为特征的分析和利用.因此,随着人工智能、生物信息学等新型应用的不断涌现,如何分析、挖掘这些新的应用中的特征,寻找这些特征与器件特性的结合点,也是此类工作未来研究的重要方向.

[1]Lee C, Ipek E, Mutlu O, et al. Architecting phase change memory as a scalable DRAM alternative[C] //Proc of the 36th Annual Int Symp on Computer Architecture. New York: ACM, 2009: 2-13

[2]Qureshi M, Srinivasan V, Rivers J. Scalable high perfor-mance main memory system using phase-change memory technology[C] //Proc of the 36th Annual Int Symp on Computer Architecture. New York: ACM, 2009: 24-33

[3]Xu Cong, Niu Dimin, Muralimanohar N, et al. Overcoming the challenges of crossbar resistive memory architectures[C] //Proc of the 21st Int Symp on High Performance Computer Architecture. Piscataway, NJ: IEEE, 2015: 476-488

[4]Hosomi M, Yamagishi H, Yamamoto T, et al. A novel nonvolatile memory with spin torque transfer magnetization switching: Spin-RAM[C] //Proc of Int Electron Devices Meeting. Piscataway, NJ: IEEE, 2005: 459-462

[5]Nigam A, Munira K, Ghosh A, et al. Model based study on energy and performance optimization for STT-RAM[C/OL] //Proc of the 2nd Non-Volatile Memories Workshop. 2011[2013-04-01]. http://nvmw.ucsd.edu/2011/

[6]Sparsh M, Vetter J. A survey of software techniques for using non-volatile memories for storage and main memory systems[J]. IEEE Transactions on Parallel and Distributed Systems, 2016, 27(5): 1537-1550

[7]Intel Corporation. Intel and Micron produce breakthrough memory technology[EB/OL]. [2018-03-03]. http://newsroom.intel.com/community/intelnewsroom/blog/2015/07/28/intel-and-micron-produce-breakthrough-memory-technology

[8]Western Digital Corporation. SanDisk and HP launch partner-ship to create memory-driven computing solutions[EB/OL]. [2017-10-12]. https://www.sandisk.com/about/media-center/press-releases/2015/sandisk-and-hp-launch-partnership

[9]Western Digital Corporation. 3D XPoint SSD pictured, performance and endurance revealed at FMS[EB/OL]. [2017-10-12]. https://www.sandisk.com/about/media-center/press-releases/2015/sandisk-and-hp-launch-partnership

[10]Cho S, Lee H. Flip-n-write: A simple deterministic technique to improve PRAM write performance, energy and endurance[C] //Proc of the 42nd Annual Int Symp on Microarchitecture. New York: ACM, 2009: 347-357

[11]Hay A, Strauss K, Sherwood T, et al. Preventing PCM banks from seizing too much power[C] //Proc of the 44th Annual Int Symp on Microarchitecture. New York: ACM, 2011:186-195

[12]Jiang Lei, Zhang Youtao, Childers B, et al. Fpb: Fine-grained power budgeting to improve write throughput of multi-level cell phase change memory[C] //Proc of the 45th Annual Int Symp on Microarchitecture. Piscataway, NJ: IEEE, 2012: 1-12

[13]Qureshi M, Franceschini M, Lastras-Montano L. Improving read performance of phase change memories via write cancellation and write pausing[C] //Proc of the 16th Int Symp on High Performance Computer Architecture. Piscataway, NJ: IEEE, 2010: 128-138

[14]Saadeldeen H, Franklin D, Chong F, et al. Memristors for neural branch prediction: A case study in strict latency and write endurance challenges[C] //Proc of the 13th Conf on Computing Frontiers. New York: ACM, 2013: 251-260

[15]Qureshi M, Karidis J, Franceschini M, et al. Enhancing lifetime and security of PCM-based main memory with start-gap wear leveling[C] //Proc of the 42nd Annual Int Symp on Microarchitecture. New York: ACM, 2009: 14-23

[16]Zhou Ping, Zhao Bo, Zhang Youtao, et al. A durable and energy efficient main memory using phase change memory technology[C] //Proc of the 36th Annual Int Symp on Computer Architecture. New York: ACM, 2009: 14-23

[17]Strukov D. Endurance-write speed tradeoffs in nonvolatile memories[J]. Applied Physics A, 2016, 122(4): 302-311

[18]Li Jing, Wu Chao, Lewis S, et al. A novel reconfigurable sensing scheme for variable level storage in phase change memory[C] //Proc of the 3rd Int Memory Workshop. Piscataway, NJ: IEEE, 2011: 141-144

[19]Li Qingan, Jiang Lei, Zhang Youtao, et al. Compiler directed write-mode selection for high performance low power volatile PCM[C] //Proc of SIGPLAN/SIGBED Conf on Languages, Compilers and Tools for Embedded Systems. New York: ACM, 2013: 101-110

[20]Zhang Lunkai, Neely B, Chong F, et al. Mellow writes: Extending lifetime in resistive memories through selective slow write backs[C] //Proc of the 43rd Annual Int Symp on Computer Architecture. Piscataway, NJ: IEEE, 2016: 519-531

[21]Zhang Mingzhe, Zhang Lunkai, Jiang Lei, et al. Balancing performance and lifetime of MLC PCM by using a region retention monitor[C] //Proc of the 23rd Int Symp on High Performance Computer Architecture. Piscataway, NJ: IEEE, 2017: 385-396

[22]Qiu Keni, Li Qingan, Xue Chun. Write mode aware loop tiling for high performance low power volatile PCM[C] //Proc of the 51st Annual Conf in Design Automation. New York: ACM, 2014: 106-111

[23]Pan Chen, Xie Mimi, Hu Jingtong, et al. 3M-PCM: Exploiting multiple write modes MLC phase change main memory in embedded systems[C] //Proc of Int Conf on Hardware/Software Codesign and System Synthesis. New York: ACM, 2014: 33-42

[24]Deng Zhaoxia, Zhang Lunkai, Chong F, et al. Herniated Hash tables: Exploiting multi-level phase change memory for in-place data expansion[C] //Proc of the 1st Int Symp on Memory Systems. New York: ACM, 2015: 247-257

[25]Qureshi M, Franceschini M, Lastrasmontano L, et al. Morphable memory system: A robust architecture for exploiting multi-level phase change memories[C] //Proc of the 37th Annual Int Symp on Computer Architecture. New York: ACM, 2010: 153-162

[26]Dong Xiangyu, Xie Yuan. AdaMS: Adaptive MLC/SLC phase-change memory design for file storage[C] //Proc of the 16th Asia and South Pacific Design Automation Conf. Piscataway, NJ: IEEE, 2011: 31-36

[27]Alibart F, Gao Ligang, Strukov D, et al. High-precision tuning of state for memristive devices by adaptable variation-tolerant algorithm[J]. Nanotechnology, 2011, 23(7): 075201

[28]Liu Xueqing, Patel V, Lukens J, et al. High-quality aluminum-oxide tunnel barriers for scalable, floating-gate random-access memories (FGRAM)[C] //Proc of Int Conf on Memory Technology and Design. Piscataway, NJ: IEEE, 2007: 235-237

[29]Yu Hung-Chang, Lin Kai-Chun, Tran L, et al. Cycling endurance optimization scheme for 1mb STT-MRAM in 40nm technology[C] //Proc of Int Conf on Solid-State Circuits. Piscataway, NJ: IEEE, 2013: 224-225

[30]Likharev K. Layered tunnel barriers for nonvolatile memory devices[J]. Applied Physics Letters, 1998, 73(15): 2137-2139

[31]Pickett M, Strukov D, Williams S, et al. Switching dynamics in titanium dioxide memristive devices[J]. Journal of Applied Physics, 2009, 106(7): 074508

[32]McPherson J, Kim J, Shanware A, et al. Thermochemical description of dielectric breakdown in high dielectric constant materials[J]. Applied Physics Letters, 2003, 82(13): 2121-2123

[33]Yang Joshua, Strukov D, Stewart D. Memristive devices for computing[J]. Nature Nanotechnology, 2013, 8(1): 13-24

[34]Mott N, Gurney R. Electronic Processes in Ionic Crystals[M]. Oxford, UK: Clarendon Press, 1940

[35]Zhang Wangyuan, Li Tao. Characterizing and mitigating the impact of process variations on phase change based memory systems[C] //Proc of the 42nd Annual Int Symp on Microarchitecture. New York: ACM, 2009: 2-13

[36]Jiang Lei, Zhao Bo, Zhang Youtao, et al. Improving write operations in MLC phase change memory[C] //Proc of the 18th Int Symp on High Performance Computer Architecture. Piscataway, NJ: IEEE, 2012: 201-210

[37]Mantegazza D, Ielmini D, Varesi E, et al. Statistical analysis and modeling of programming and retention in PCM arrays[C] //Proc of Int Electron Devices Meeting. Piscataway, NJ: IEEE, 2007: 311-314

[38]Awasthi M, Shevgoor M, Sudan K, et al. Efficient scrub mechanisms for error-prone emerging memories[C] //Proc of the 18th Int Symp on High Performance Computer Architecture. Piscataway, NJ: IEEE, 2012: 15-26

[39]Joshi M, Zhang Wangyuan, Li Tao. Mercury: A fast and energy-efficient multi-level cell based phase change memory system[C] //Proc of the 17th Int Symp on High Performance Computer Architecture. Piscataway, NJ: IEEE, 2011: 345-356

[40]Jung C, Lee E, Min K, et al. Compact verilog: A model of phase-change RAM transient behaviors for multi-level applications[J]. Semiconductor Science and Technology, 2011, 26(10): 105018

[41]Kim K, Ahn S. Reliability investigations for manufacturable high density pram[C] //Proc of the 43rd Annual Int Symp on Reliability Physics. Piscataway, NJ: IEEE, 2005: 157-162

[42]Choi Y, Song I, Park M, et al. A 20nm 1.8v 8GB PRAM with 40mb/s program bandwidth[C] //Proc of the 59th Int Conf on Solid Circuit. Piscataway, NJ: IEEE, 2012: 46-48

[43]Zebchuk J, Srinivasan V, Qureshi M, et al. A tagless coherence directory[C] //Proc of the 42nd Annual Int Symp on Microarchitecture. New York: ACM, 2009: 423-434

[44]Zhao Hongzhou, Shriraman A, Dwarkadas S. SPACE: Sharing pattern-based directory coherence for multicore scalability[C] //Proc of the 19th Int Conf on Parallel Architectures and Compilation Techniques. New York: ACM, 2010: 135-146

[45]Kelm J, Johnson M, Lumettta S, et al. WAYPOINT: Scaling coherence to thousand-core architectures[C] //Proc of the 19th Int Conf on Parallel Architectures and Compilation Techniques. New York: ACM, 2010: 99-110

[46]Sánchez D, Kozyrakis C. SCD: A scalable coherence directory with flexible sharer set encoding[C] //Proc of the 18th Int Symp on High Performance Computer Architecture. Piscataway, NJ: IEEE, 2012: 129-140

[47]Fang Lei, Liu Peng, Hu Qi, et al. Building expressive, area-efficient coherence directories[C] //Proc of the 22nd Int Conf on Parallel Architectures and Compilation Techniques. New York: ACM, 2013: 299-308

[48]Sanchez D, Kozyrakis C. The ZCache: Decoupling ways and associativity[C] //Proc of the 43rd Annual Int Symp on Microarchitecture. New York: ACM, 2010: 187-198

[49]Zhang Lunkai, Strukov D B, Saadeldeen H, et al. SpongeDirectory: Flexible sparse directories utilizing multi-level memristors[C] //Proc of the 23rd Int Conf on Parallel Architectures and Compilation Techniques. New York: ACM, 2014: 61-74

[50]Ramos L, Gorbatov E, Bianchini R. Page placement in hybrid memory systems[C] //Proc of the 25th Int Conf on Supercomputing. New York: ACM, 2011: 85-95

[51]Deng Zhaoxia, Zhang Lunkai, Chong F, et al. Memory cocktail therapy: A general learning-based framework to optimize dynamic tradeoffs in NVMs[C] //Proc of the 50th Annual Int Symp on Microarchitecture. New York: ACM, 2017: 232-244

[52]Zhang Mingzhe, Zhang Lunkai, Liu Zhiyong, et al. Quick-and-Dirty: Improving performance of MLC PCM by using temporary short writes[C] //Proc of the 35th Int Conf on Computer Design. Piscataway, NJ: IEEE, 2017: 585-588

[53]Kang D, Baek S, Mutlu O, et al. Amnesic cache manage-ment for non-volatile memory[C] //Proc of the 31st Symp on Mass Storage Systems and Technologies. Piscataway, NJ: IEEE, 2015: 1-13

[54]Liu Renshuo, Yang Chia-Lin, Wu Wei. Optimizing nand flash-based SSDs via retention relaxation[C] //Proc of the 10th Int Conf on File and Storage Technologies. Berkely, CA: USENIX Association, 2012: 115-126

[55]Liu Renshuo, Shen Deyu, Wang Chengyuan, et al. NVM Duet: Unified working memory and persistent store architecture[C] //Proc of the 19th Int Conf on Architectural Support for Programming Languages and Operating Systems. New York: ACM, 2014: 455-470

[56]Jung J, Cho S. Memorage: Emerging persistent RAM based malleable main memory and storage architecture[C] //Proc of the 27th Int Conf on Supercomputing. New York: ACM, 2013: 115-126